- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DDC和DUC的大带宽DRFM设计与实现

摘要 介绍了采用DDC和DUC技术实现的大带宽DRFM及其基本原理,并在Matlab中进行了理论仿真,使用QuartusⅡ完成了对整个系统及内部模块的建模,最后在Modelsim中进行了整个系统的功能仿真,为今后DRFM技术的研究提供理论和技术支持。

关键词 数字射频存储器;数字下变频;数字上变频

随着超高速、超大规模集成电路的出现,数字下变频(Digial Down Converter,DDC)技术和数字上变频(Digital Up Converter,DUC)技术得到快速发展,使得DRFM系统的瞬时带宽得以提升,其中,采用正交调制解调技术的DRFM,瞬时的带宽可达到600 MHs以上,基本可覆盖一般雷达信号的带宽,甚至覆盖一般雷达信号的所有工作带宽。由此,使得雷达对抗技术进入一个新的发展空间。

1 大带宽DRFM基本原理

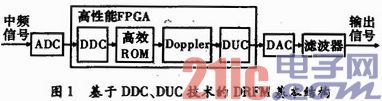

基于DDC和DUC技术的大带宽,DRFM的基本原理是:由雷达天线接收战场的雷达信号,将接收到的雷达信号,经过高速的ADC变换器进行采样量化,转变为中频数字信号,然后经过DDC把ADC变换器输出的中频数字信号变为零中频信号,并将其进行快速存储。再将高速ROM中的数据读出,对其进行多普勒(Doppler)频移变换,使得最后输出信号比原信号多—个多普勒频移量,从而使输出信号可以模拟假目标信号的多普勒效应。再将多普勒频移后的信号经过DUC做上变频处理,将零中频信号搬到中频,其中DUC过程的各项参数设置与DDC中的各项参数完全一致,以保证能够完全恢复出中频信号的频带和相位信息,最后将输出的数字中频信号经过DAC变换器恢复为射频模拟信号,并送给发射天线进行发射。基于该原理的DBFM基本结构如图1所示。

2 大带宽DRFM信号仿真

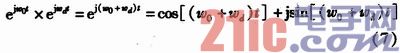

系统将雷达接收到的射频雷达信号,经过高速A/D变换器采样量化后得到中频数字信号,送入基于多相滤波原理实现的DDC模块,得到基带I、Q两路信号。然后与复信号![]() 进行复乘法运算,实现信号的多普勒频移,将得到的信号经过DUC模块处理后上变频为中频信号,再经过DAC输出,从而实现整个DRFM系统的功能。

进行复乘法运算,实现信号的多普勒频移,将得到的信号经过DUC模块处理后上变频为中频信号,再经过DAC输出,从而实现整个DRFM系统的功能。

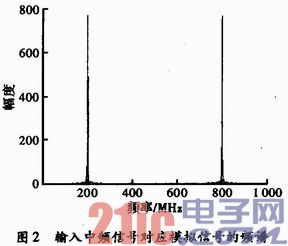

设输入中频信号fIE对应的模拟信号x(t)=a(t)cos[2πfot+φ(t)]=a(t)cos[2π(f1+f2)t+φ(t)],假设振幅a(t)=1,初相φ(t)=0,中频信号的载波频率f1=750 MHz,基带信号频率f2=50MHz。中频模拟信号对应的信号频谱如图2所示。

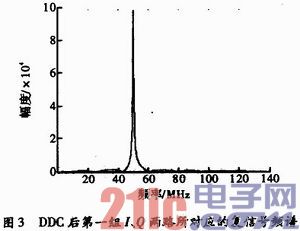

图2显示输入信号频率为800 MHz,前面200 MHz的频谱是模拟信号对应复频率-800 MHz,经过采样率为fs=1 000 MHz的采样,频谱进行周期性搬移后,在正半轴产生的镜像频率。中频信号经过DDC模块后的频谱如图3所示。

如图3所示,将中频信号经过数字下变频(DDC)模块处理以后,得到的I、Q两路的信号对应的复信号的频谱已经为基带信号50 MHz。

假设DDS模块产生的正交信号频率fd=62.5 MHz,DDC模块输出的基带信号经过多普勒频移后,得到第一组I、Q两路信号对应复信号的频谱如图4所示。

图4所示,频率从基带的50MHz搬移到了112 5 MHz,完成了预想的结果。

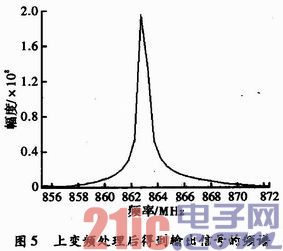

将得到的信号进行数字上变频(DUC)处理,即经过与DDC的相反过程后,得到输出信号的频谱如图5所示。

图5所示,信号频率从112.5 MHz搬移到了862.5 MHz,而载波频率为750 MHz,基本与理论一致。即输入的800 MHz中频信号经过DRFM系统后转变为862.5 MHz,得到的结论与实际预想相同,完成了DRFM系统的功能。

3 大带宽DRFM在FPGA中的设计与实现

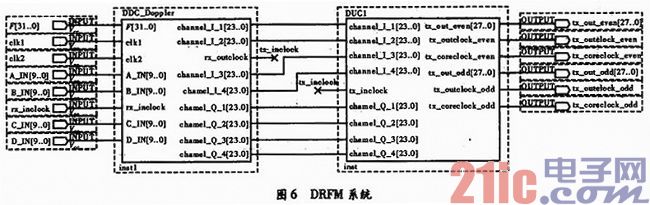

根据上述DRFM系统的基本结构,在FPGA开发平台QuartusⅡ中实现其功能,主要完成对系统及内部模块的建模,并在Modelsim中对整个系统进行了功能仿真,验证了设计的正确性。在FPGA中实现的基于DDC和DUC大带宽DRFM的整体模块如图6所示。

如图6所示,在高性能FPGA中主要实现的是数字下变频,多普勒调制和数字上变频3部分。图中的第一模块实现数字下变频和多普勒调制,第二模块实现数字上变频。以下分别介绍3个部分在FPGA中的具体实现。

3.1 FPGA中DDC模块的实现

设计中采用了基于多相滤波结构的数字正交下变频(DDC),首先介绍基于多相滤波结构的DDC算法。

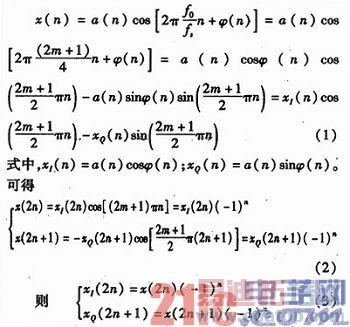

设输入中频信号为x(t)=a(t)cos[2πfot+φ(t)],按以下采样频率fs对其进行采样,由带通采样原理可知,m=0,1,2,…。其中m取值满足fs≥2B的最大正整数。

得到的采样序列为

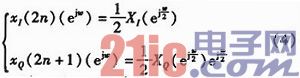

即x(2n)(-1)n和x(2n+1)(-1)n两个序列分别是同相分量xI(n)和正交分量xQ(n)的2倍抽取序列。根据抽取原理可知,如果xI(n)和xQ(n)的数字谱宽度<π/2,则其两倍抽取序列xI(2n)和xQ(2n+1)可以无失真表示原序列。根据傅里叶变换性质可以推出

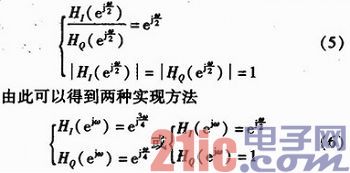

可知两者的数字谱恰好相差一个延迟因子*,在时域上即是相差0.5个采样点。为弥补这种时域的非对齐,需要引入两个时延滤波器加以校正。这两个滤波器需满足

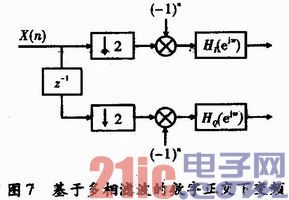

基于多相滤波的数字正交下变频实现过程如图7所示。

由上述算法,可以推导出宽带DDC的多相滤波高效结构如图8所示。

输入中频数字信号为x(n),依次经过一个采样点的延迟后分别进行4倍抽取,得到4路并行信号,依次为a(n)、b(n)、c(n)、d(n)。将得到的4路并行信号,分别经过一个采样点的延迟后再分别进行2倍抽取,得到8路并行信号,依次为x0(n)、x1(n)、x2(n)、x3(n)、x4(n)、x5(n)、x6(n)、x7(n)。由式(3)可知,x(n)的偶数项对应其同相分量I路信号,奇数项对应其正交分量Q路信号。于是,对以上的8路信号进行处理,得到4路并行的I路信号xI0、xI1、xI2、xI3和4路并行的Q路信号xQ0、xQ1、xQ2、xQ3,其中xI0=x0(n)、xI1=x2(n)、xI2=x4(n)、xI3=x6(n)、xQ0=x1(n)、xQ1=x3(n)、xQ2=x5(n)、xQ3=x7(n)。将得到的4路并行的I路信号与4路并行的Q路信号分别通过满足式(5)的时延滤波器,使得I路信号和Q路信号在时域上对齐。经过时延滤波器后,得到I路4路并行信号xII0(n)、xII1(n)、xII2(n)、xII3(n),和Q路4路并行信号xQQ0(n)、xQQ1(n)、xQQ2(n)、xQQ3(n)。

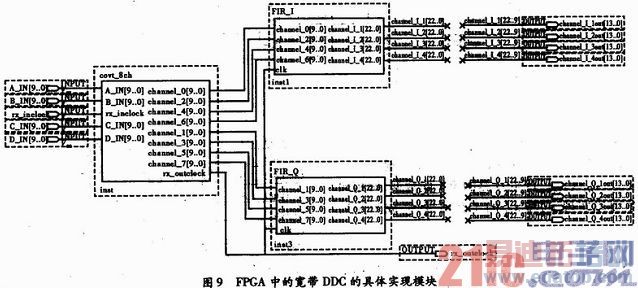

虽然信号x(n)经过抽取后变成了8路信号,经过DDC后变成了4路并行的I路和Q路信号,尽管每一路保存的I、Q两路信号对应的复信号与原信号相比,都有一定的频谱损失,但这4路并行的信号总体却完整保存了信号x(n)的频谱和相位信息。若要恢复信号x(n),只需经过一个相反过程即可。该宽带DDC的多相滤波结构在FPGA中具体实现的模块如图9所示。

图9中第1模块实现将信号x(n)抽取变为8路信号,分离出I路和Q路数据。第2,3模块实现的是将并行4路的I路和Q路数据经过各自对应的滤波器实现时域上的对齐,并最终将中频数字信号变成基带信号。

3.2 FPGA中Doppler模块的实现

多普勒调制原理

根据多普勒调制的原理,对经过DDC模块后产生的基带信号进行多普勒调制。文中采用直接数字频率合成(DDS)产生正交本振信号cos(2πfdt)和sin(2πfdt)两路信号,对其分别进行4倍抽取,得到xDI0、xDQ0,xDI1、xDQ1,xDI2、xDQ2,xDI3、xDQ3这4路信号。

将得到的x(n)4路同相分量xI(n)和正交分量xQ(n)分别与DDS产生的4路并行的I、Q两路正交本振信号做复乘法运算,即xOI0=xII0×xDI0-xQQ0×xDQ0,xOQ0=xQQ0×xDI0+xII0×xDQ0,下面做相同变换,得到对应的xOI和xOQ的4路信号,从而实现4路信号的多普勒频移。

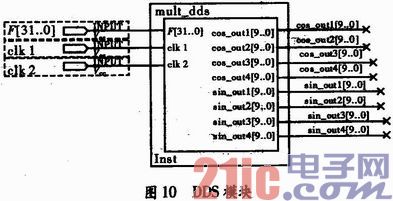

用于产生4路并行的I、Q两路正交本振信号的DDS模块如图10所示。

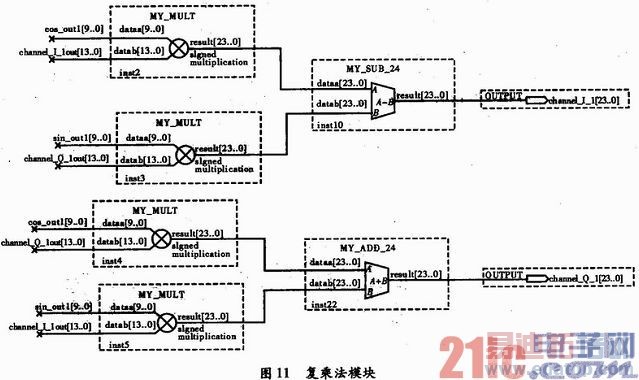

图10中输出的分别为4路并行的I路数据和4路并行的Q路数据。将其与DDC输出的4路同相分量xI(n)和正交分量xQ(n)做复乘法运算。后续实现多普勒频移的复乘法模块如图11所示。

图11中的第1部分实现xOI0=xII0×xDI0-xQQ0×xDQ0,产生I路的第1路数据,第2部分实现xOQ0=xQQ0×xDI0+xII0×xDQ0,产生Q路的第1路数据,做相同的处理,可以实现xOI和xOQ的4路信号,完成多普勒调制。

3.3 FPGA中DUG模块的实现

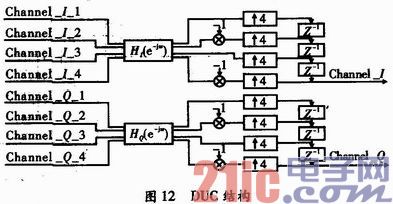

DUC模块的工作过程与DDC模块相反,是DDC的一个逆过程。即为多普勒调制输出的4路并行的I路和Q路数据,分别经过滤波器![]() ,还原I、Q两路在时域上的非对齐性,然后各自完成4倍的内插,实现数字上变频,其结构如图12所示。

,还原I、Q两路在时域上的非对齐性,然后各自完成4倍的内插,实现数字上变频,其结构如图12所示。

该数字上变频在FPGA中的具体实现模块如图13所示。

3.4 系统在Modelsim中的仿真

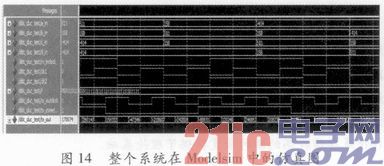

将FPGA中的整个系统在Modelsim中进行仿真,结果如图14所示。

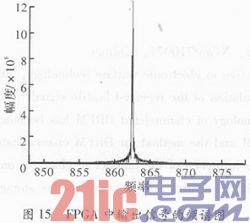

将图14得到的输出信号的离散的值导入到Matlab中,查看其频谱图,如图15所示。

如图15所示,输出信号频率为862.5 MHz,与图5仿真结果相同,由此得出,在FPGA中的整个DRFM系统实现的功能与理论上得到的结果一致,从而完成了DRFM系统的功能,达到了预期的效果。

4 结束语

随着超宽带高分辨率雷达在未来战场发挥的作用越来越大,对于超带宽雷达的干扰技术研究,将成为雷达对抗领域的重要研究方向。文中针对基于现代化软件无线电原理的数字下变频(DDC)和数字上变频(DUC)技术,对实现的DRFM系统进行了分析及系统仿真,得出的结论与预想结果吻合良好,证明了系统的可行性。