- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高性能数字接收机FPGA设计

摘要:基于Xilinx FPGA设计出一种高性能数字接收机。该数字接收机由高速、高分辨率A/D和高性能FPGA构成。高速A/D实现中频数字化,高性能FPGA实现数字下变频、数字多相滤波、半带抽取、匹配滤波和位同步功能,使得中频载波为153.6MHz的TD-SCDMA信号,下变频-抽取-滤波-位同步后得到高质量的采样率为1.28MHz的基带信号。在中频放大器工作时,接收机的动态范围达到84dB,即A/D有效分辨率到13bit,EVM小于1%,满足TD-SCDMA综测仪的测试用例要求。

引言

软件无线电是近些年在移动通信领域中流行的一种通信系统设计架构。基本思想是:用软件设计的方法构造一个开放性、标准化和模块化的通用平台,设计出具有高度灵活性、开放性的移动通信系统。

基于软件无线电的设计思想,数字接收机是根据奈奎斯特带通采样定理(欠采样原理)利用A/D转换器将中频(IF)信号数字化,并在数字域中采用IQ正交下变频方法将载波信号移除,得到高采样率的零中频基带信号,再经过多级滤波、抽取(下采样)、匹配滤波、位同步等步骤将调制信号的采样率降到合适水平给后级处理,以减轻DSP数据吞吐量的压力。

本设计来源于国家科技重大专项"三模综测仪"子项目开发的TD-SCSMA部分;该数字接收机主要完成目标是实现数字信号处理的多速率变换,采样率从122.88MHz降低到1.28MHz,线性动态范围优于84dB,IQ两路信号带宽为1.6MHz。

电路设计

数字接收机架构

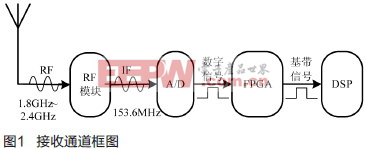

由于FPGA(XC5VSX95T)具备高速并行计算优势,数字接收机方案设计通常由A/D转换器+高性能FPGA+DSP构成。接收通道原理框图如图1所示。

移动终端的射频范围覆盖1800MHz~2400MHz,射频信号与本振信号混频后,经过滤波转变成固定载波频率的153.6MHz中频信号。根据带通采样定理,A/D以122.88MHz时钟对153.6MHz中频信号进行采样、量化、编码,数字化后的信号以122.88Msps速率传输给FPGA。最后在FPGA中实现30.72MHz的NCO与A/D发送的信号混频以得到零中频基带信号,此时,数据的采样率仍很高,需要进行多速率抽取滤波转换、最佳采样点的判断和位同步处理。

数字下变频原理

根据奈奎斯特带通采样(欠采样)定理的公式:

其中,Fs表示A/D采样频率,Fc表示载波中频频率,B表示信号带宽。