- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

整合型MIMO收发器 提升微型/微微型基站系统性能

MIMO (多重输入输出)运用技术和射频的波束成型技术已被证明是在宽带无线接入(BWA)系统上,可达到最高数据吞吐量和高频谱利用效率的技术。在这些系统中,关键点是对已知射频路径的调相,并同时对所有信号取样。

为了满足这些要求,系统设计人员通常使用一个属于单一本地振荡器(LO)来源的共同参考频率,并分给两个独立的通道。基站接收器的线性规格和发射器的误差矢量振幅值(EVM)规格,以往会要求混合式的实作形式,纳入各级整合方块,并选择个别的高性能低噪声放大器(LNA)、混频器、增益方块和转换器,以满足系统的目标。

在具有2RX×2TX能力的现代积体组件上,其性能水平已经足以将这些系统的实作,包括高性能的内建接收器、发射器、合成器和转换器都共存于一个组件上。

事实上,整合组件的性能已经从以客户端设备(CPE)定位的产品,到微微型基站及微型基站(Pico and Micro-basestation)性能水平的产品,并且迅速接近完整基站的性能水平。高性能2×2整合组件已经面世,并且是用来实现射频同步的最佳选择,因为如此便可共享组件上所有的资源。

为了发挥MIMO概念的优点,系统规划人员定义4×4、8×8,甚至更复杂的配置。随着系统复杂度增加,同步化的工作也随之增加,材料清单亦然。本文介绍了整合型收发器如何通过减少复杂度、组件数量和成本来简化设计,并同时能够实现出色的微微型基站及微型基站系统性能。

整合型收发器有利同步系统要求

为了产生所要求的射频波束成型样式,两个射频信号之间的固定关系必须存在于MIMO系统所有信道的两两之间。传统上用来建立这些关系的方法是分配共享合成器的输出给接收方块和发射方块,这样它们都会具有完全相同的调相,确切的路径可以特征化并校准,使通道之间的相位差可以求得。一旦建立了关系,波束成型技术可以用来实现所要求的接收或发射样式。

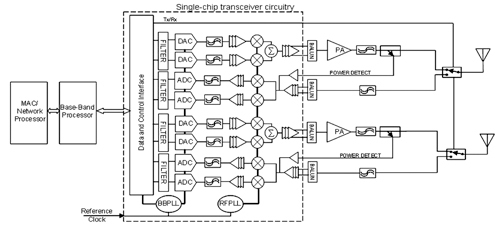

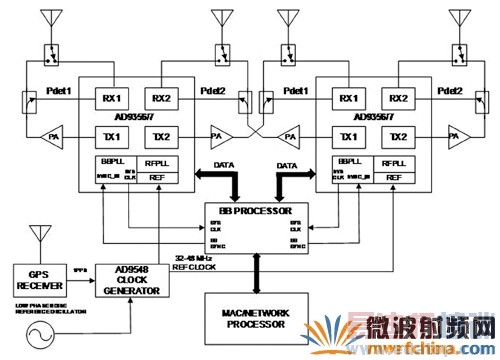

对于2×2的MIMO系统而言,整合收发器的选择显示于图1的虚线框内,可以用来有效实现同步系统。接收器和发射器的组件都有一个共同的LO路径,以便信道的调相在任何时候都是固定的。

图1 2×2 MIMO基站架构

在4×4或8×8(甚至信道更多)的系统,基带处理器使用的参考信号,其同步化须要实现整个系统的一致性。使用全球卫星定位系统(GPS)锁定频率发生器来同步化基带频率将会在相关的文章中探讨,但同步化这个基本的问题也会在这里解决,因为同步基带和射频两者,同样会用来同步整合的系统。

基带同步为射频调相技术关键

所有的组件被同步到相同的参考频率还必须参照一个在射频信道上已知的相位。正如刚才提到的整合解决方案包含必要的LO产生电路,这样就可以简单利用内建的资源简化2×2的系统。然而在高阶系统,射频同步化的任务更加复杂。

每个组件的信道合成器利用其自身的锁相回路(PLL),产生一个误差信号来强制让原本频率自由振荡的压控振荡器(VCO)对准到所需的频率。将多个整合组件的VCO同步化,使它们的相位一致是非常困难的。正因为如此,给所有组件共享一个外接LO会消除这些问题。可以外接LO的组件显然最适合这样的任务。

单芯片2×2的MIMO组件,如业者已推出包含同步化电路,用来调整基带合成器的频率边缘。此外,该组件除了能够对射频输出信号进行取样之外,还包含外接LO的能力。有了基带同步化以及已知射频输出信号的相位,应用射频调相技术的功能便可以设计出来。

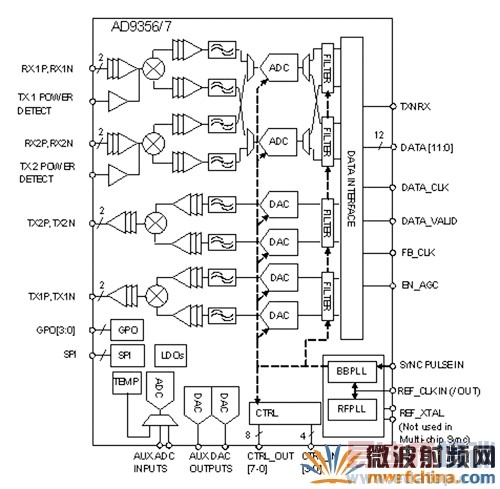

图2显示业者所推出单芯片2×2的MIMO组件的简化方块图。要产生给定系统的一个特定取样率,会使用一个N分频PLL,可在40MHz的范围内的任何参考频率中,合成出基带频率参考信号。对于2×2的系统,参考频率可以是内含的或外接的。基带频率是在两个接收器和两个发射器之间共享,所以并不须要另外设计同步化功能。同样的,射频LO是共享的,所以RX和TX信号的相位一致性则是与生俱来。

图2 单芯片2×2的MIMO组件方块图

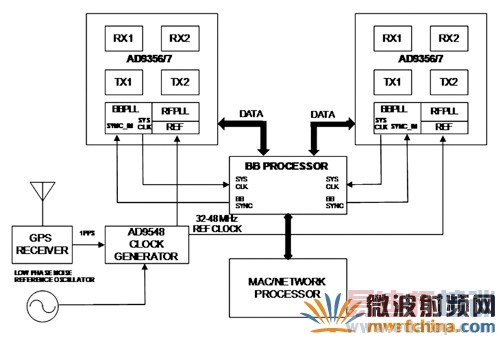

对于4×4及具有更多信道的基站系统,通常可用GPS锁定外部参考频率,因此所有收发器组件都会假定有这个功能并加以利用。从基带控制器发出同步化脉冲的应用上,组件的基带PLL被有计划的重置,因而达到基带频率的相位对准。在图3中是个两组件的示意图,但是可以用更多的组件以相同的方法串接下去。

图3 业者推出的基带多芯片同步示意图

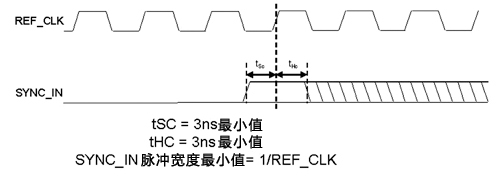

选择具有所需数据速率的整数倍参考频率频率,将使得BBPLL运行在整数模式,所以不会发生N分频合成才会有的抖动。例如图4说明了对于一个标准的全球微波存取互通接口(WiMAX)10MHz通道,取样率需要的是11.2MHz,所以会使用频率44.8MHz的外接振荡器。SYNC_IN脉冲的时序相对来说就不算太严格。

图4 MIMO组件基带多芯片同步SYNC_IN脉冲时序

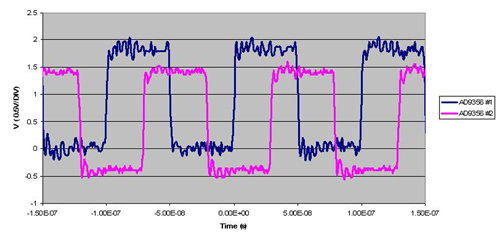

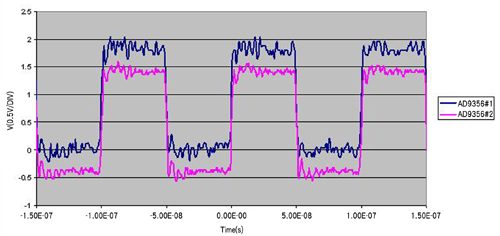

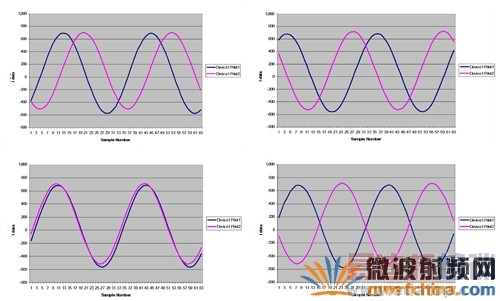

BBPLL的同步,可以通过在示波器上观察每颗芯片的BBPLL频率输出来检查。它们在同步程序完成后就会重叠。借着配置单芯片2×2 MIMO组件的某一支可程序输出接脚作为BBCLK,便可以很容易地以基带控制器,或是在示波器上显示,将BBPLL同步测量出来(图5、图6)。

图5 在同步之前单芯片2×2的MIMO组件IC1与IC2的频率信号图(初始阶段为随机)。

图6 在同步之后,单芯片2×2的MIMO组件IC1与IC2的频率信号(相位对齐)

业者推出的两款产品VCO,结构差别在于已开启信道信号的产生方式。一个在VCO产生信道频率的两倍频如在2.5GHz操作下,其VCO频率为5GHz。另一组件则是VCO产生信道频率的四或三倍频如在3.6GHz操作下,其VCO频率为4.8GHz。内部合成器提供约-40dB(1%)EVM的卓越性能,但这两颗芯片也已经可以使用外接LO来源,因为,如此一来,便可以得到更高的性能。如果使用一个适当的低噪声外接LO信号,EVM性能可提高到优于-45dB(0.56%)。

在多芯片系统,需要多重天线波束成型如4TX×4RX,这时共同外接LO就可以保证组件间的相位一致性。如前所述,应用于前述两种组件上的LO信号不是直接用作信道频率。这里用到的LO在芯片上被分给自行运作的分频器,用来产生已开启通道的LO。因此,简单地采用外接LO就不用同步,但两个组件之间的调相,仍可以通过交叉耦合(Cross-coupling)现有的功率检测器,很容易地测定出来,然后一起比较两个接收信道的数据样本。在VCO频率是倍频的组件中,所以产生的TX信号,其相位不是同相就是超出180度。而另一组件采用了四或三倍频的VCO/信道频率关系,由此产生的TX信号相位将会是四种可能值之一,不是0度,就是90、180或270度。在4TX乘4RX系统下,要测定TX信号相位的电路连接图介绍见图7。

图7 MIMO组件用于4Tx乘4Rx连接的射频相位测量图

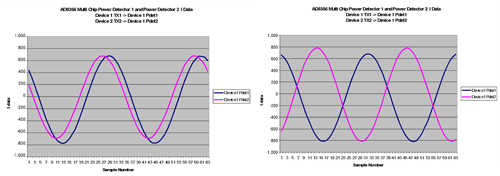

若使用VCO频率是倍频的组件,其结果如图8。该图是画出由接收通道1取样到的I值到由接收通道2取样到的I值,接收通道1是连接到同一个芯片的某一个发射器输出端,而接收通道2则是连接到系统中另一个芯片的某一个发射器输出端。在第一张图中,很容易测定该LO分频器是与TX信号同相,只在时间轴上有略微的偏移。在第二个图中,也很容易测定两组件之间的TX信号大约超出相位180度。在这些组件中,LO分频器是自行运作的,因此相位不能预先测定,然而一旦进行测量,且产生信号的相位是已知的,正确的偏移补偿可用于实现波束成型算法。同理,采用了四或三倍频的VCO/信道频率组件中,其四个可能的相位如图9所示。

图8 MIMO组件射频相位测量I的数据,左图为0度、右图为180度,外接LO驱动。与理想相位之间的偏移是由于轻微的电线长度不匹配。

图9 另一组MIMO组件射频相位测量数据,其射频相位为0、+90、-90和180度都有可能,因为是用合成器输出分频器,并外接LO驱动。为每个新的工作频率下的调相都会测量到,并保持下去。

由于组件使用直接转换,这个通过功率检测器和通过接收器测量的信号,须要从信道的中心被偏移。这些组件包括了能够生成偏移连续(Continuous Wave, CW)音,在这里是指TestTone的功能,方便进行相位测量。当基带频率同步时,TestTone将在两个组件上产生同样的相位。很容易依照所产生数据样本的结果来做直接比较和相位测量。

使用交叉耦合发射器,以同样的方式,系统可以利用这一技术来测定芯片之间的调相,以建立任何N×N规模的MIMO数组。对于成本非常敏感的应用,交叉耦合技术在利用芯片内建合成器的情况下,还是可以应用在组件上。虽然内部LO的相位不像外接LO的情况下可以预测,但仍然可以用同样的方式测量,在给定频率的命令之下,组件之间的相位关系仍将保持不变。这对要求成本效益更高的解决方案还是有帮助的,而相较于最佳EVM的解决方案,只有些微不利的影响。

宽带无线接入基站使用了MIMO和射频波束引导技术,以实现最大的覆盖范围和细胞负载量。成功实作的关键是测量RF信号相位的能力与基带取样频率的同步。

整合型收发器的性能已经取得重大进展,使其可以用在新的设计中。使用上述的技术,通过整合型组件可节省的可观电力、重量、组件数量以及最重要的成本,这些应用产品便可以达到优越的性能。

作者:Rick Myers,ADI半导体公司

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:GPS接收机射频前端电路原理与设计

下一篇:如何解决射频设计中的热问题