- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

3G及LTE升级 加速发射器RFIC整合

| 随着次世代移动通讯基础架构设备由3G及长期演进(LTE)Advance升级,为设备与元件供应商带来了许多的挑战。针对全球性的部署,次世代无线电必须能够在更多的运作频率波段上,对更高的资料速率以更复杂的调变支援更广的信号频宽。有关杂讯、信号线性度、功率消耗及尺寸大小的性能都极为重要,而且要求也越来越高,因此元件供应商也被寄予厚望能为更高密度的应用降低成本与空间。 | ||||||

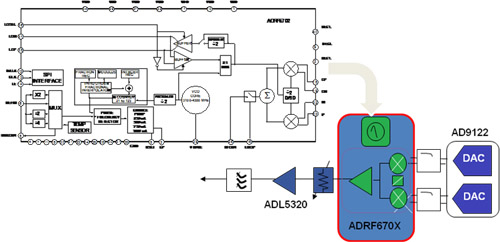

这点为无线射频集成电路(RFIC)的设计厂商带来更多的挑战,因为经过整合后的元件,其性能必须相当于或优于分离式方案。使用分离式元件的实现方案时,系统设计厂商可以选择使用经过最佳化的元件,并且采用不同的技术像是砷化镓(GaAs)、矽双极(Si Bipolar)或互补式金属氧化物半导体(CMOS)等,为最佳化的性能进行设计(图1)。但是这种选择最佳化制程技术的弹性,对于想要在单一制程技术中提供更高整合度的RFIC设计厂商会带来最大的挑战。

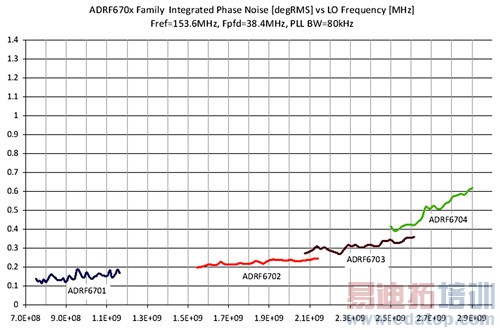

在基地台发射器当中,类比式I/Q调变器乃是决定发射信号路径杂讯层以及线性度的主要RFIC元件,因此任何为了缩小尺寸、降低功率或成本而要求放宽性能都是不可接受的。 BiCMOS制程可两全其美 幸好,矽锗(SiGe)双极互补式金属氧化物半导体(BiCMOS)制程技术特别适合使用于较高整合度,而且又不会牺牲性能。这些制程通常用于多重临界速度(Speed-breakdown)SiGe NPN电晶体,有时候也会用于具有一个或两个(较常见)CMOS电晶体特征尺寸的互补式高性能PNP电晶体。在此基底会加上MIM(金属-绝缘体-金属)电容器、薄膜电阻,以及很重要的多重厚铜箔与铝金属涂布。这些特点让设计厂商能够在单一晶片中设置多个高性能功能区块,进而实现强固的能力及缩小尺寸,并且维持极高水准的性能。 在发射器电路板级设计上的几个重要元素中,有一项就是针对不同的上升与下降频率转换级本地振荡器(LO)的合成及分配。基地台LO分配必须对印刷电路板中所有远距离的角落都保持相位的一致性,而且也必须具有低带内与低宽频杂讯,以及低总体寄生内容。混频器的性能只会与驱动用的LO相当,因此在总体发射器性能中,高品质的LO是一项极为重要的元件。此外,非常小量的相位杂讯,或是LO信号中的杂散成分,有可能会将足够的能量引导至类比信号路径中,进而造成发射器无法符合主要的蜂巢式通讯标准如MC-GSM 、宽频分码多重存取(WCDMA)、LTE、全球微波存取互通介面(WiMAX)所设定的杂散辐射(Spurious Emissions)。这些标准所需的LO,范围从大约500MHz到接近4GHz,代表的意义是对于LO分配的布局必须非常谨慎地处理。从LO产生一直到最后的终止端,走线的长度应该要越短越好,但是假如LO合成器必须馈送至数个不同元件,则往往难以实现。有一种解决方案是将共通的低频参考信号馈送至靠近每一组所需LO的独立锁相回路(PLL)合成器中,但将会在印刷电路板(PCB)上占用显著的面积。 矽锗技术提供高性能 ADRF 670x整合式调变器系列将先进的分数N型PLL与整合式压控振荡器(VCO)加以整合,解决掉许多这类型的难题。透过矽锗技术的使用,在正交调变器及具有VCO的混频器上实现了技术领先的动态范围,提供具有竞争力的性能,而且明显地比外部VCO/PLL解决方案还要小。 VCO的运行是在上层的厚金属层中,借以在晶片电感器内建立high Q,作为电感电容槽的一部分。 VCO电容器乃是利用金属氧化物半导体(MOS)可切换式MIM电容器所组成,这使得VCO可以在广大的频率范围中以低相位杂讯切换频率。 每当PLL频率被加以编程时,波段会自动地调整,借以提供独立而且可靠的解析度。选择波段的大小以确保作业在初始设定完成后,能够于完整的温度范围中运作。厚金属也被用来针对下一级的期间,将输出balun(平衡/非平衡转换器)与绝佳的回授损失予以整合。 ADRF 670x家族系列由四颗具有重叠性的成员所组成,能够涵盖从400M~3GHz的频率范围与波段。每组家族成员都是依据输出blaun频宽,在1dB和3dB带通上加以设定的。 ADRF 670x和ADRF 660X家族的分数N型PLL设计,很适合使用在低相位杂讯的3G与4G应用领域中。这些新的蜂巢式标准具有密集间隔的信号丛集,因而需要日益增加的较低LO整合式相位杂讯,以便维持完整的性能。传统的PLL合成器设计会采用「整数N型」架构,其输出频率为一组整数乘以相位侦测器的频率。为了要能够在频率上提供小步阶尺寸,其整数的倍增系数必须很大。大量的LO相位杂讯会从参考路径中产生,并且被PLL频率倍增系数放大。这将会在PLL输出上造成高带内杂讯。分数N型PLL能够实现小步阶尺寸的输出频率,同时可以维持较低的总体频率倍增,进而比整数N型PLL具有较低的相位杂讯放大(图2)。

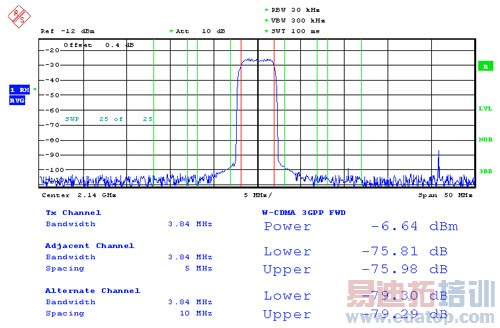

相邻通道功率比(ACPR)乃是一项用来判定有多少发射信号漏泄至相邻频率波段的测量。如WCDMA之类的3G标准,对于容许发射至波段外的功率量非常严格。针对ADRF 6702的ACPR测量如图3所示。调变器提供高线性度的输出功率与低杂讯,在-6dBm输出下可以达成优于-76dB的ACPR。这将有助于减少紧接于调变器后增益级的数量,并且在最终功率放大器级之前就将动态范围最大化。

ADRF 670X系列家族藉由将三组LDO电路予以整合,使运作能够脱离5伏特的单一电源供应,进一步地将使用者应用装置简化,并且减少成本与电路板空间。 这些LDO是用来为VCO、电荷帮浦及PLL积分三角调变器提供经过调整的电源,而+5伏特电源供应则直接使用在e IQ调变器上,借以将输出功率最大化。 在高线性度的应用装置当中,ADL 670X可以利用其PLL在内部合成一组LO,而其他元件则可以停用本身的PLL,并且使用来自于主要元件的共通LO。 多重组合打造次世代平台 ADRF 670X家族乃是为了要实现最小化以及简化与亚德诺(ADI)最新的发射用数字类比转换器AD 9122和砷化镓放大器的使用者介面所设计,后者若以一颗四分之一瓦高线性度放大器ADL 5320为例,则能够驱动大于0dBm至最后PA级。这种结合三颗精巧IC的做法实现了主动式IC的内容,很适合使用于所有的蜂巢式次世代多重载波无线电平台。 (本文作者Phillip Halford为亚德诺射频产品行销经理、Ed Balboni为射频设计经理) |