- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

分析有线电视和通讯应用的PIN二极管衰减器的结构

用两个并联电阻和一个串联电阻就可以构造一个基本的pi配置固定电压衰减器,通过配置即可以得到A=20log (K)的衰减,同时提供能够匹配具体应用电路特性阻抗的输入/输出阻抗。在工作频率高于衰减器截止频率的情况下,一个PIN二极管可以做为电流控制可变电阻使用。在工作频率10倍于fc时,一个PIN二极管就可以精确地用一个具有恒定微值结电容的电流控制并联电阻来模拟。工作频率低于0.1fc时,PIN二极管就表现为一个普通的PN结二极管。

工作频率在0.1fc到10fc之间时,PIN二极管的特性就变得非常复杂,一般表现为一个与一个高频电流电感或电容并联的、随频率变化而变化的电阻。另外,工作在这个范围内时,信号失真畸变也非常严重。对于HSMP-3810型二极管而言,τ≈1500ns,其截止频率为1,000kHz,因此在1000kHz以上二极管的电阻值与工作频率无关,不过,由于已经针对宽带衰减器应用对此二极管进行了优化,所以即使在fc以下此二极管也具有良好的特性。

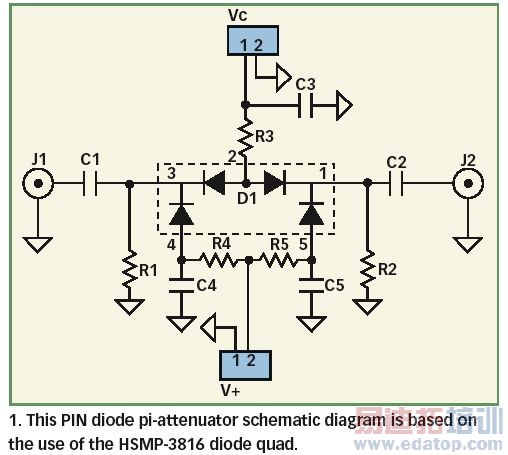

可以用三个二极管来代替pi电路中的固定电阻,构造一个可变衰减器,不过,这样会导致网络中的不对称,从而导致产生一个相当复杂的偏压网络。用两个PIN二极管来代替其中的串联电阻可以获得几个性能方面的好处。首先,由于串联二极管具有容性电抗而使网络与其它部分相隔离,用两个二极管代替一个电阻可以提高最大衰减值或在一定衰减值的条件下使频率上限翻倍。其二,代替串联电阻的两个二极管是180度反接的,这样就抑制了偶数次信号畸变的产生。其三,由此而得到的衰减器网络是对称的,从而可以大大简化偏压网络。电源电压V+是一固定电压,Vc是控制网络衰减的可变电压,用两个二极管代替电阻的唯一缺点是可能会增加介入损耗。

四元二极管pi型衰减器需要一个恒定的电压V+和一个可变的控制电压Vc。对于1.25V的V+,可变控制电压的范围为0V到大约5V。电压V+的值代表了回程损耗与控制电压范围之间的一个折衷,更低的V+可以降低回程电压,但同时也会使控制电压的工作范围缩小。

衰减器是在指定的频率范围内,一种用以引入一预定衰减的电路。一般以所引入衰减的分贝数及其特性阻抗的欧姆数来标明。在有线电视系统里广泛使用衰减器以便满足多端口对电平的要求。如放大器的输入端、输出端电平的控制、分支衰减量的控制。衰减器有无源衰减器和有源衰减器两种。有源衰减器与其他热敏元件相配合组成可变衰减器,装置在放大器内用于自动增益或斜率控制电路中。无源衰减器有固定衰减器和可调衰减器。

衰减器的工作频带是指在给定频率范围内使用衰减器,衰减器才能达到指标值。由于射频/微波结构与频率有关,不同频段的元器件,结构不同,也不能通用。现代同轴结构的衰减器使用的工作频带相当宽,设计或使用中要加以注意。

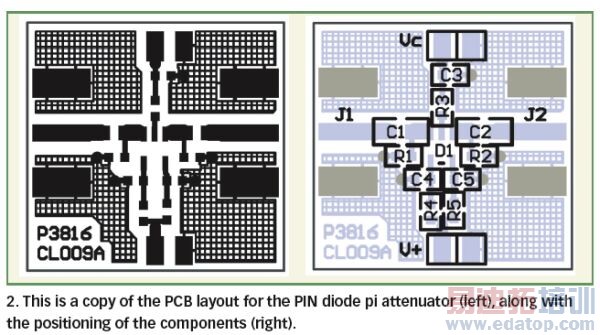

本文中介绍的衰减器是在8mm厚的RF4型印刷电路(PCB)上实现的。RF4具有良好的机械稳定性和耐久性,成本低,但其损耗大,难于控制,而且介质系数与工作频率密切相关。另一方面,玻璃纤维增强型聚四氟乙烯(PTEE)PCB材料具有良好的高频特性,但是相对昂贵一些,机械稳定性也比较差,不适合于某些表面贴装工艺。选用针对高频工作要求进行了优化的PCB基底材料可以改善高频性能,各种测量参数对频率的依赖程度受到与HSMP-3816二极管四元组、PCB、其它元件及连接器相关的寄生效应的影响。

将PIN二极管用做衰减元件时,PIN二极管具有比等效的GaAs MESFETs更高的线性度,通过使用具有厚I层及低介质张弛频率(fdr)的多个PIN二极管就可以将信号畸变减小到最低程度。在Avago公司PIN二极管产品线中HSMP-381x系列产品的I层最厚。在低衰减状态,大部分RF能量仅仅是从输入端传输到输出端而已。它们接近于零偏压状态,其结电容将随RF电压同步变化,幸运的是,由于两个二极管是反向串联的,所以可以抑制由受RF调制的电容所产生的某些失真或畸变。由于封装的两个反串二极管具有完全互相匹配的特性,因此可以得到最佳的失真抑制能力。

普通的二极管由PN结组成。在P和N半导体材料之间加入一薄层低掺杂的本征(Intrinsic)半导体层,组成的这种P-I-N结构的二极管就是PIN 二极管。正因为有本征(Intrinsic)层的存在,PIN 二极管应用很广泛,从低频到高频的应用都有,主要用在RF领域,用作RF 开关和RF保护电路,也有用作光电二极管(PhotoDiode)。PIN 二极管包括PIN光电二极管和PIN开关二极管。

PIN二极管还可以调节到高频范围。为改善隔离特性,我们可以将两个或多个二极管串联起来,但同时会引起介入损耗的增大。PIN二极管本质上还属于电流控制的电阻器。为减少介入损耗,它们需要采用大量的直流电源以降低I(本征)区内的电阻率。这显然会影响电池寿命。这种特点,再加上PIN二极管方案需要大量器件,使得这种技术很难应用于便携手持式产品。

Pi衰减器的相位偏移随衰减值而变化。总的相位偏移接近90度,在三个相隔较远的工作频率点(100、900和1800 MHz)测试时此相位偏移表现相当稳定。

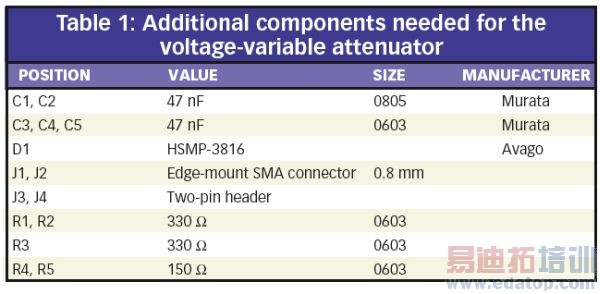

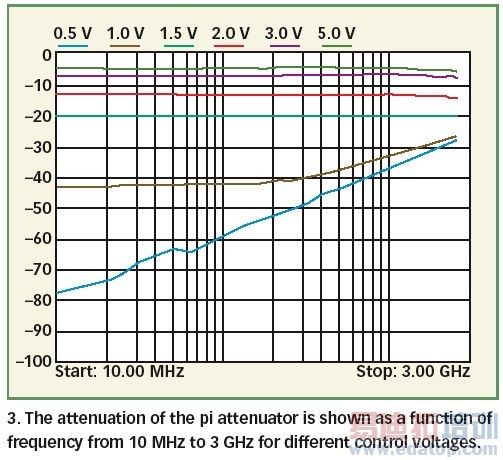

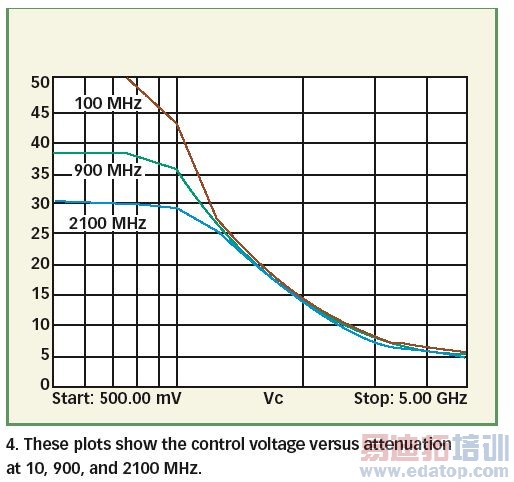

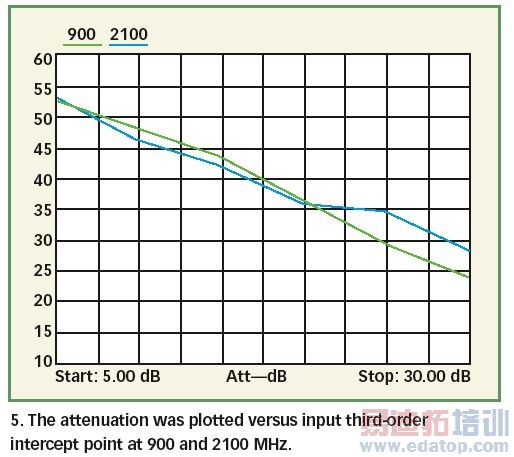

图1所示为π衰减电路的示意电路图。图2的左边为π衰减器的PCB布局,右边为元件布置。表1中给出了所需要的元件(包括四元二极管)。图3、4、5给出的成品π衰减器测试性能的样本。

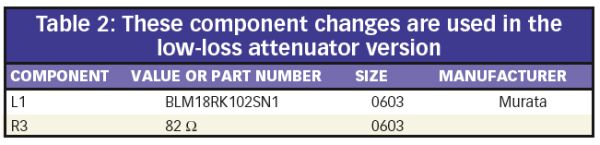

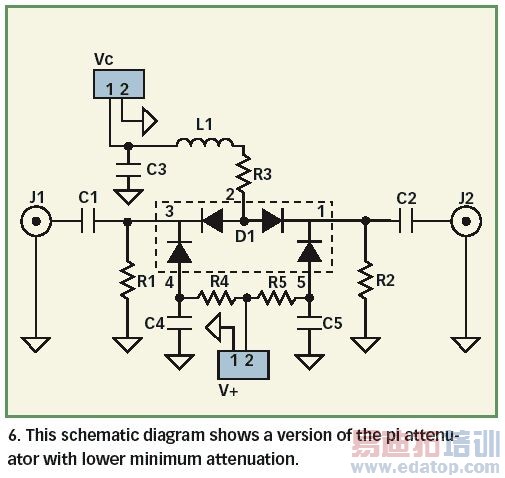

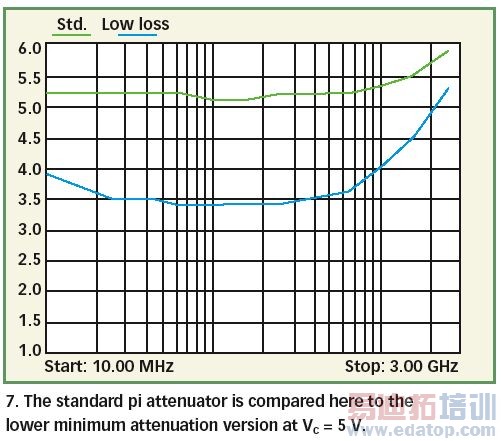

增加通过串联二极管的电流可以降低衰减下限。将控制电压保持在最大值5V,减小电阻R3的阻值就可以增大偏移电压,这可以通过给阻断RF的电阻R3(表2)串联一个表面贴装铁酸盐珠状电感而实现。在整个频率范围内,与传统的瓷芯多层片状电感相比,这种铁酸盐珠状电感具有更高的阻抗。图6给出了低衰减下限衰减电路的示意图,图7中给出了在Vc=5V的条件下与标准衰减电路的比较结果。

为了建立π衰减器的性能模型以便于进一步分析,安捷伦公司的高级设计系统(ADS)计算机辅助工程(CAE)软件为工程师们提供了模拟四元二极管π衰减器性能的技术支持范例。

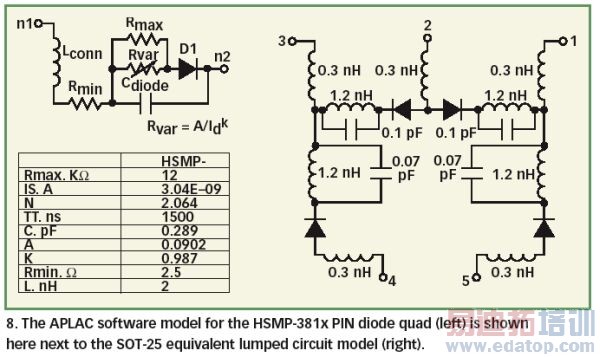

另外,包含在高频建模工具APLAC CAE软件包中的PIN二极管模型也可以预测在给定正向偏移的条件下RF阻值。图8的左边给出了HSMP-3816 PIN二极管的APLAC模型,将APLAC模型与SOT-25等效电路模型(图8右边)结合在一起,就可以使设计人员在模拟过程中研究分析封装的寄生效应。