- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

射频走线与地的那点事儿

举个例子来说吧。我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示(两种线宽):

图1a:线宽0.1016 mm的射频线(表层铺地前)

图1b:线宽0.35 mm的射频线(表层铺地前)

图1:表层未铺过地的PCB

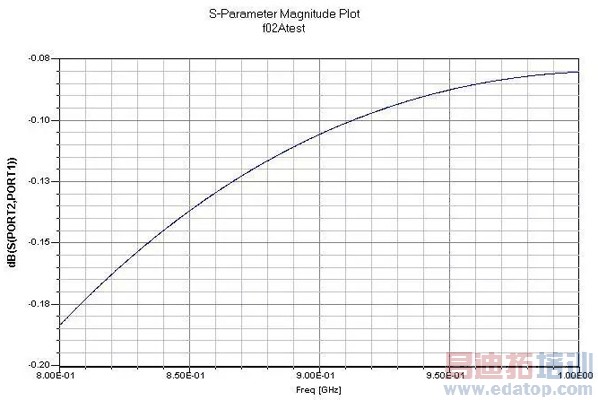

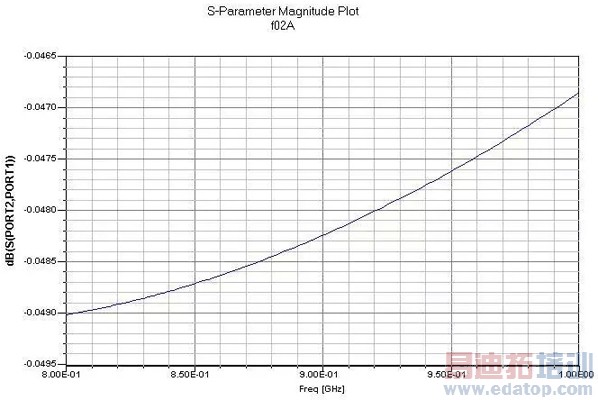

首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

图2a:表层未铺地的S21 (线宽0.1016mm)

图2b:表层未铺地的S21 (线宽0.35mm)

图2:表层未铺地的S21

由图中可以看到,在800MHz-1GHz的范围内,仿真的数据展示为小数点后一到两位的数量级,0.35mm的损耗要比0.1016mm的线小一个数量级,这是因为0.35mm的线宽在该板的层叠条件下其特征阻抗接近50Ω。 因此间接验证了我们所做的阻抗计算(用线宽约束)是有一定作用的。

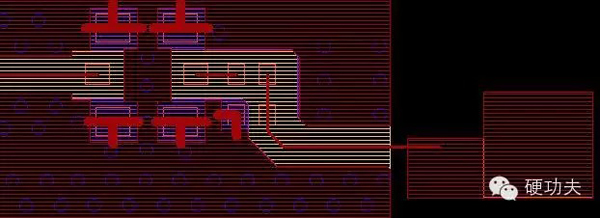

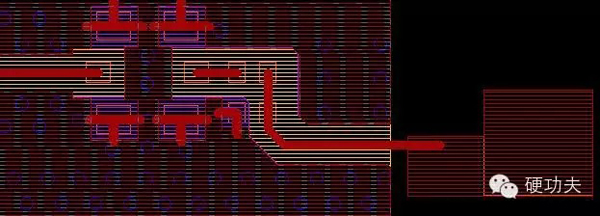

接下来我们做了表层铺地后的同样的仿真(800MHz-1GHz),导入的PCB文件如下图。

图3a:0.1016 mm的射频线(表层铺地)

图3b:0.35 mm的射频线(表层铺地)

图3:表层铺过地后的PCB

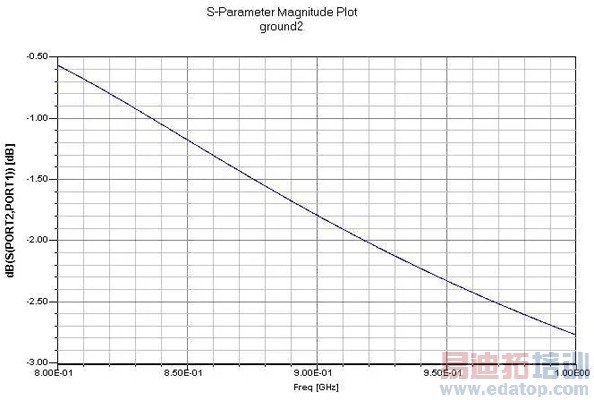

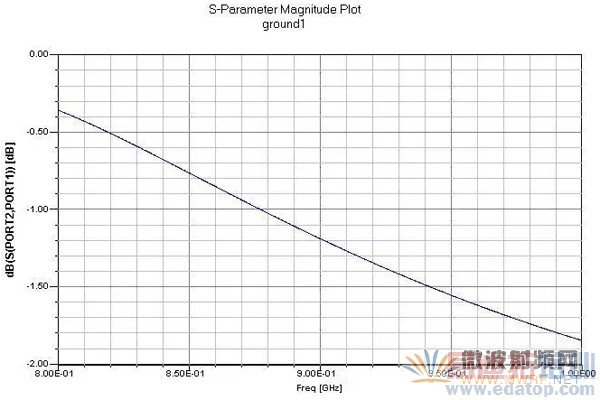

仿真结果如下图:

图4a:表层铺地后的S21 (0.1016mm)

图4b:表层铺地后的S21 (0.35mm)

图4:表层铺过地后的S21

由图中看到,仿真的数据显示,该传输线的线损已经是1-2 dB的数量级了,当然0.35 mm的损耗要明显小于0.1016 mm的。另外一个明显的现象是相对于未铺地的仿真结果,随着频率由800MHz到1GHz的增加,损耗趋大。

我们可以从仿真的结果中得到这样一个结果:

1.射频走线最好按50欧姆走,可以减小线损;

2.表层的铺地事实上是将一部分RF信号能量耦合到了地上,造成了一定的损耗。因此PCB表层的铺地应该有所讲究。尽量远离RF线。工程经验是大于1.5倍的线宽。

作者:射频居士 微信号硬功夫

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:使用EDA分析PCB

下一篇:基于Matlab的均匀平面电磁波的仿真