- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

选型要素:射频接收芯片结构的“秘密”

录入:edatop.com 点击:

一般而言,在现代的射频系统中,天线接收到的信号频率很高而且具有极小的信道带宽。如果考虑直接滤出所需信道,则滤波器的Q值将非常大,而且高频电路在 增益、精度和稳定性等方面的问题,在目前的技术条件下,对信号直接在高频段解调是不现实的。使用混频器将高频信号降频,在一个中频频率进行信道滤波、放大 和解调可以解决高频信号处理所遇到的上述困难,但是又引入了另一个严重的问题,即镜像频率干扰:当两个信号的频率与本振(LO)信号频率差在频率轴上对称 地位于本振信号的两边,或者说它们的绝对值相等但是符号相反,那么经过混频后这两个信号都将被搬移到同一个中频频率。如果其中一个是有用信号,另一个是噪 声信号,那么噪声信号所在的频率就称为镜像频率,这种经过混频后的干扰现象通常被称为镜频干扰。

为了抑制镜频干扰,普遍采用的方法是利用滤波器滤除镜像频率成份。但是由于该滤波器工作在高频频段,其滤波效果取决于镜频频率与信号频率之间的距离,或者说取决于中频频率的高低。如果中频频率高,信号频率与镜像 频率相距较远,那么镜像频率成份就受到较大的抑制;反之,如果中频频率较低,信号频率与镜像频率相隔不远,滤波的效果就较差。但另一方面,由于信道选择在 中频频段进行,基于同样的理由,较高的中频频率对信道选择滤波器的要求也较高。所以,镜像频率抑制与信道选择形成了一对矛盾,而中频频率的选择成为平衡这 对矛盾的关键。在一些要求较高的应用中,常常使用两次或三次变频来取得更好的折衷。

依靠考虑周到的中频频率选择和高品质的射频(镜像抑制) 和中频(信道选择)滤波器,一个精心设计的超外差接收机可以达到很高的灵敏度、选择性和动态范围,长久以来成为经典的传统选择。如前所述,超外差接收机在 抑制镜像频率干扰、敏度和选择性上有较大优势,而且多级转换无直流漂移和信号泄漏,但是也有成本高、对IR滤波器有较高要求、需要低噪声放大器(LNA) 和混频器(Mixer)与50W的良好匹配等缺点,而且镜像频率抑制滤波器和信道选择滤波器通常不适于单片集成。

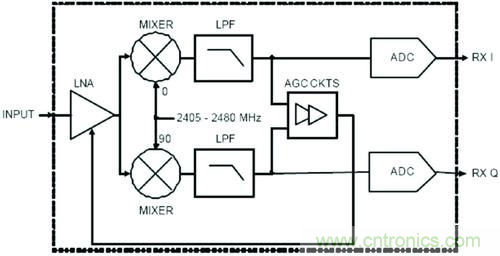

后来的零中频(Zero IF)结构,如图1所示,不需要抑制滤波器,交互调制降低,较适合单片集成。但也有直流失调、信号泄漏的缺点,而且需要高频、相噪的频率合成器,给电路设 计也带来一定难度。与零中频相似,低中频(Low IF)结构也适于集成,其结构如图2所示(两图均以2.4GHz频段的IEEE802.15.4协议为例)。但需要注意的是带内镜像频率信号的抑制。通常 需要70dB的镜像抑制比,但往往片上集成只能达到40dB或更少。

图1 零中频接收机结构;低中频接收机结构

其他接收结构还有宽带-双中频接收机、采样接收机、数字中频接收机等。宽带-双中频接收机结构具有易集成、成本低、功耗低等优点,其缺点是闪烁噪声影响和二 阶互调失真明显,且有射频中频串扰的问题。子采样接收机和数字中频接收机对模数转换器(ADC)有较高要求,如需要ADC有足够高的动态范围,带通Σ-Δ ADC( Band pass Σ-Δ ADC)等,而带通Σ-Δ ADC有较大的设计难度。

如前所述的原因,现在的射频芯片采用零中频和低中频方案的设计较为普遍,也是射频接收端通常需要仔细评估的两种方案。零中频采用IQ解调的方法提取相位,正交成分等信息,由ADC将其数字化后处理。低中频则采用典型的限频鉴频器从调制载波中提取信号。

低中频结构避免了自动增益控制(Automatic gain control, AGC)电路且对信道信号的好坏有较快的响应速度,由此降低了接收机及相关电路的复杂度。鉴频器等电路易于设计,不要求载波同步及大电流,占用芯片面积也 较小。不过相对于采用相干解调的零中频结构,低中频结构的灵敏度会有3dB的损失。而且通常低中频结构需要一个信道滤波器获得有效载波频率,降低噪声,邻 道干扰等的影响。如果射频系统所使用的协议所限定的信号频率宽度,邻道选择要求较宽松,则对滤波器的要求就比较低。低中频结构还需要镜像抑制混频器降低镜 像干扰问题。

对于低码元(chip)率的协议,如2M Chips/s,要求调频宽度约为2 MHz。如果中频过低,信道滤波器相对带宽过高,那么滤波器也很难实现,而且也难以将中频信号滤出,则将难度转嫁给了基带的数字滤波器。相反,中频滤波器频率过高就要求放大器的带宽足够大。

相比于低中频,零中频结构不需要本振在接收和放射模式间改变频率,也就降低了频率合成器设计的难度。零中频结构也不需要镜像抑制混频器,因为零中频结构不会 产生镜像频率。相比于相等带宽的中频带通滤波器的设计,零中频结构只需要更简单的低通滤波器以确定I路与Q路输出信噪比。零中频结构可以在滤波器匹配和同 步检波技术上获得最佳解调效果。

不过零中频相比于低中频技术也有自身的缺点。比如需要AGC,混频器后的直流偏移(DC offset)消除电路,并且由于信号分I、Q两路,故须两个模数转换器(ADC)及一个共用的ADC来对信号进行模数转换。IQ两路与基带芯片或集成的 基带电路之间需要一个IQ模拟接口,IQ结构存在一个重要设计难点就是IQ平衡问题。IQ两路间的幅值和相位失衡将产生IQ图像叠加在有用信号上,这会降 低EVM性能。所以,零中频结构有时还需要额外的电路来隔离基带芯片以实现同步解调。表1给出在一种IEEE802.15.4的射频接收器在0.18mm 工艺下的两种设计方案的面积对比。

总之,接收器结构设计非常重要,不能简单的认为哪种结构“好”哪种结构“不好”,而是需要认真的分析协议要求,根据相关参数仿真,而且最终的定案会牵涉到多方面的折衷考虑。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:网友解析:公共WiFi为何不安全?

下一篇:揭秘:高速信号发生的关键所在