- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速先生:案例分享之DDR3不能运行到额定频率

某客户有一个板子需要新增一部分功能,想将原来的小板改为大板,但出于成本考虑,又将原来的8层板改为了6层板,板子做出来后在实际测试时DDR3只能降频到400MHz才能稳定工作,而之前的8层板可以稳定工作在533MHz,这两版的电源供给情况基本一致,主控及DDR3芯片的型号和批次也是一致的。客户也是比较有经验的,做过多种尝试如调整驱动及ODT等都没有改善,后来就找到了我们。

原因分析:大家都知道,一般DDR3运行不到额定的频率最直接的影响因素就是时序,时序裕量太小或不足都会导致系统工作不稳定或根本就运行不上去。而影响DDR3时序的因素主要有以下几点:电源噪声、串扰、等长匹配、信号质量等。只要上面几大点没出什么问题,DDR3出问题的几率也会相对少很多(前提是硬件原理和软件配置没问题)。下面我们就针对各种因素来各个击破,这种时候用排除法是比较好的。

电源噪声:电容分布基本上是0.1uF的电容,无其他容值的电容,适当增加几个大容值电容在低频的时候效果更好,但测试电源噪声只有20mV左右,量级比较小,所以电源噪声的影响可以初步排除。

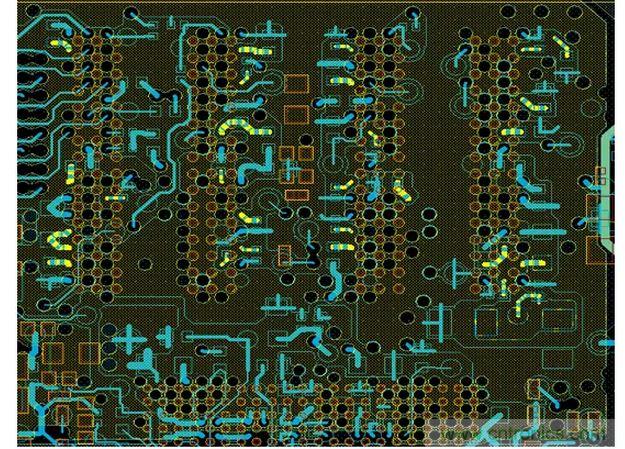

串扰问题:数据信号间距10.55mil,地址信号10mil;信号之间的间距为2H(W),线路中心距离为3H(W),若空间允许,间距可以适当加大。

信号与旁边的电源地网络不能太近,需要避免(小问题)

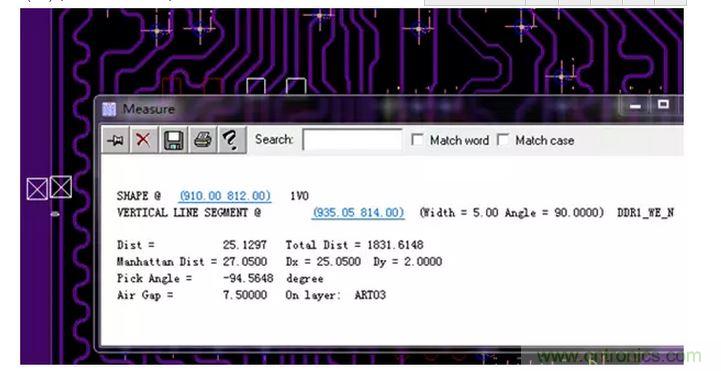

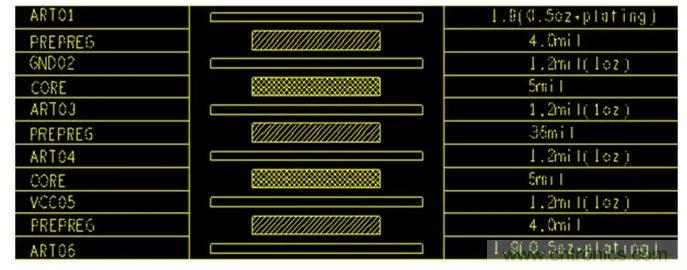

由于是3、4层内层走线,但从叠层看3、4层之间的间距已足够大,串扰问题影响比较小。

信号质量问题:此板DDR3地址、命令信号用了外部的上拉电阻,另外客户也已经调整过芯片驱动及ODT功能,所以信号质量问题也不大。

等长匹配问题:

1、主控芯片是否有write and read leveling(读写平衡)。经查此主控芯片为国内芯片厂家研发的,一般国产芯片需要格外注意,由于读写平衡功能需要购买额外的IP,而注重成本的国产芯片为了降低成本,结果就可想而知了,具备此功能的芯片就相对的比较少了。那没有了这个功能,我们的DDR3通常就按照DDR2的约束规则来布线(就事论事,没有贬低国产芯片的意思,事实上我们都要支持国产哈,支持国产,从你我做起,希望国货越来越强!)。

2、重点关注数据组与时钟(地址)的等长匹配。

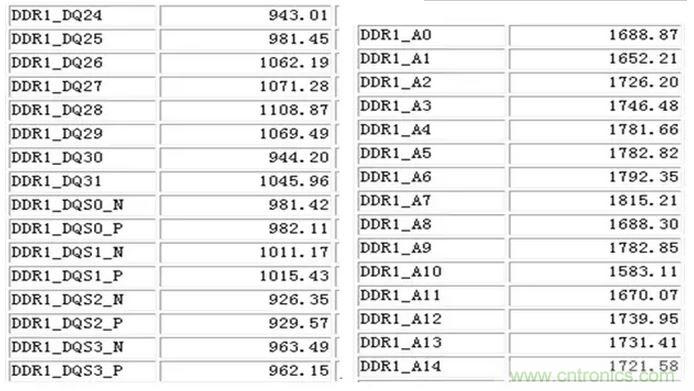

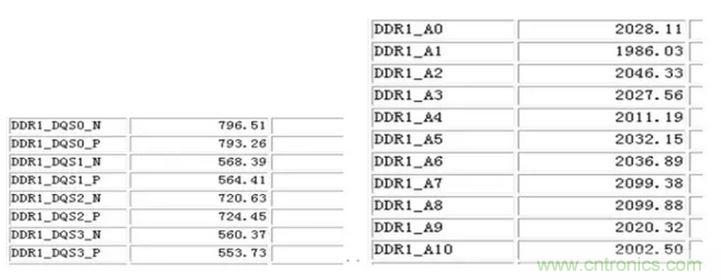

正常工作的板子走线长度如下所示,地址与时钟的长度相差200mil内:

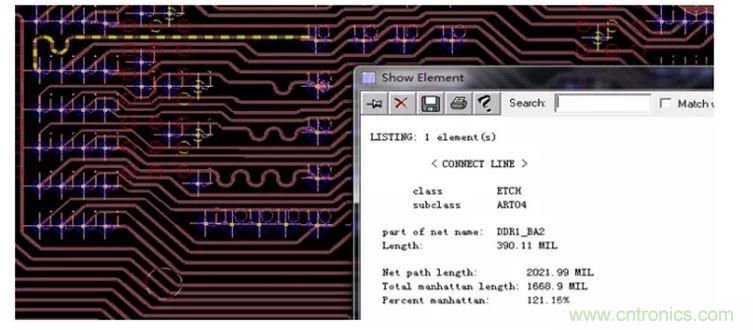

有欠缺的板子走线长度如下所示。

•数据组内做了严格等长,地址、控制、时钟也做了等长,但数据与时钟相差较大,如下所示。

•地址信号平均总长度2000mil减掉一个分支长度400mil,大致可以知道主控到其中一个颗粒的长度在1600mil,而数据信号最短的长度才550mil,之间相差比较大,超过了1000mil。

这也是前后两版差异最大的地方,由于主控芯片没有读写平衡功能,再加上由之前的8层板改成了6层板,布线空间的减少就使得我们的工程师没有过多的去绕线,而系统不能自动调整数据与时钟的偏差,最终导致时序裕量不够,这应该就是DDR3运行不到额定频率的主要原因。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:阻抗匹配根本无法与孔径调谐匹敌,原因何在?

下一篇:是什么因素影响天线的互调结果?