- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

再也不用担心抖动和电流!高端时钟缓冲器的设计

录入:edatop.com 点击:

几乎所有的电子系统都需要针对一个或多个处理器以及许多相关外围IC的多个时钟信号,以建立该系统的运行节奏。这些时钟信号通常由石英晶体产生,频率范围可以从几MHz到几百MHz。

虽然许多集成电路都需要这些时钟信号,但在大多数设计中采用多个晶体作为主时钟源并不现实,也不是所期望的方式。其原因是,使用多个独立的时钟源会带来这些时钟与靶标同步的问题,提高了系统成本,同时增大了对于电路板面积的要求。相反,设计者几乎总是选择使用一个单一的主时钟振荡器作为时钟源,再将时钟信号分配给整个系统中的各个组件。

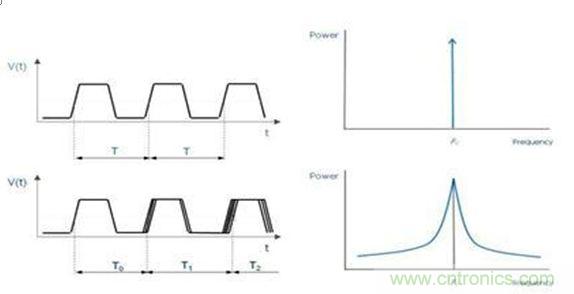

但这种解决方案也不是没有挑战。首先,所有的时钟都不是完美的,每个时钟,即使是在一个精心设计的振荡电路中的一个精准晶体,也会围绕其标称频率产生一些相关的抖动和微小的时序变化,如图1a所示,这相当于在频域中的相位噪声,见图1b。

主时钟的固有缺点只是问题的开始。时钟振荡器通常不能支持所有必须的负载,也不能驱动连接信号源与负载之间的电路布线或电缆。

[page]

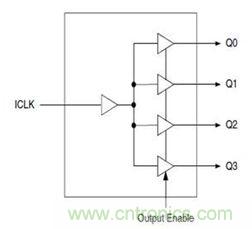

为了克服这一驱动能力的不足,需要一个专门的时钟缓冲器IC用于在树状拓扑架构下升压和“扇出”主时钟,如图2所示。缓冲器功能简单,并只完成一项工作:它以时钟源作为其输入,并且提供能够尽可能完美复制时钟输入的多个输出。

尽管这种功能往往不是很引人注目,也不可能得到太多的关注和重视,但它在系统整体性能、信号完整性、以及系统和电路的一致性、可靠性方面起着重要作用。目前市场上有可以驱动2个、4个、8个甚至更多负载的缓冲器IC,能够紧密配合设计的需要,无需额外的成本费用或电路板空间,如图3所示。

采用一个缓冲器:简单,但不是没有挑战

理想的时钟缓冲器能够传输得到升压的输入时钟,但不能有任何附加的抖动、延迟、失真、或其他不利因素。像所有其他组件一样,这种理想的时钟缓冲器并不存在,而一些器件却可以很接近、非常接近理想情况。显然,缓冲器会占据PCB空间、消耗功率、并增加成本,它们还会把自身的抖动增加到时钟的内在抖动上。但现实中没有可行的替代方案,因此,我们的目标必须是要获得与应用良好匹配的时钟缓冲器。

这里重要的是要理解为什么缓冲器的低抖动如此至关重要。从网络设备、高端PC到仪器设备,当今许多电子产品所允许的抖动指标非常小。很多这些产品的典型抖动值约为100fs(飞秒,为10-15秒,或十亿分之一秒的百万分之一),比几年之前认为是高性能的指标高出一个量级。

一般情况下,缓冲器的抖动远比时钟的抖动要小,所以主要抖动源是时钟,而不是其缓冲器。缓冲器输出驱动的所有负载的复合抖动是时钟和缓冲器抖动值的均方根(rms)组合。例如,一个时钟具有抖动400fs(均方根值),其缓冲器抖动为50fs(均方根值),结果只有5fs的有效附加均方根抖动,所以缓冲器对于组合均方根抖动的贡献比时钟小很多。(请注意,这里只是抖动的一个顶级特性,抖动是一个多方面的、非常复杂的问题;见附文“抖动表征和测试。”)

对于抖动期望在收紧

既然缓冲器对于整体抖动的贡献如此之小,为何还要关心使用更好、具有更低抖动的缓冲器呢?简言之,当今电子产品的系统时钟速度发展趋势和要求在影响所需的参数。随着系统性能和时钟速度提高,时钟必须比上一代产品有更低的抖动。其结果是,具有更低抖动的时钟缓冲器对于保证负载端的性能要求非常重要。

通过对粗略数字的基本分析可以使这一点更加清晰。在时钟和缓冲器的抖动相等时(这种情况在时钟抖动不断缩小时可能发生),得到的抖动均方根值为√2(≈1.4)比单独的时钟要高,几乎增加50%以上。其结果是,各个负载端的时钟信号性能与时钟的原始值相比显著降低。因此,随着时钟性能变好,具有更低的抖动时,关键是要降低缓冲器的抖动,甚至更多,这样缓冲器对于整体抖动的贡献可以最小化。

传统上,电路设计者对于过度抖动问题的解决途径需要在缓冲器性能参数之间进行不令人满意的折衷。他们可以选择具有低抖动的缓冲器,但要做到这一点,这些缓冲器要消耗更高的电流和/或电压。简而言之,更低的抖动需要更大的电流。不幸的是,这意味着缓冲器用户陷入较高功耗、更多低能效组件的困境,从而降低了电池供电产品的运行时间,增大了散热量,这些都是不依赖于电源以及是否有足够的散热措施都必须要考虑的。

现在的好消息是,这种传统的折衷已经不再需要。IDT公司全新系列的时钟缓冲器基于经过验证的IC工艺,同时采用了设计和拓扑结构方面的创新,实现了极低的抖动但功耗并没有增加,同时还具有更小的芯片尺寸,能够采用一系列的电源轨供电运行。例如,IDT5PB11xx系列LVCMOS扇出缓冲器在12kHz到200MHz范围内具有低于50fs的均方根附加相位抖动,而内核电流只有15mA。

[page]

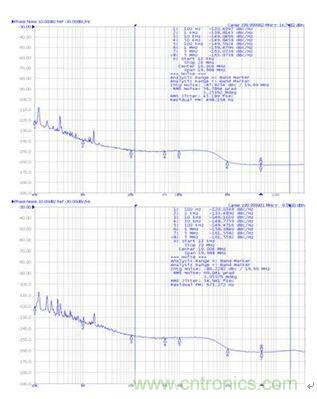

通过仔细分析在此频率范围内的均方根附加相位抖动曲线可以更明显地看到这些得到的好处。图4a展示的是在5PB11xx缓冲器输入端来自于200-MHz时钟源的抖动,而图4b则示出了相同的参数,但是在缓冲器输出端。即使在最高频率(这是最具挑战性的区域)时,附加抖动仅为31.6fs。IDT公司产品系列的其他器件具有不同的输出扇出和配置变化,但都具有类似的低附加抖动。

除了独特的低抖动、低功耗特性外,IDT5PB11xx缓冲器也具有其它性能优势。它可以采用1.8V到3.3V之间的宽范围电压供电运行,而性能不会降低。因此在一个具有多个电源轨的较大设计中,可以在不同的地方采用同样的部件,甚至在多个产品中采用同一部件。这不仅简化了物料清单(BOM),同时也降低了因使用多个新部件而导致出现的附加性设计“意外”自然风险。

5PB11xx的信道与信道输出偏移(skew)(输出信道之间的相对时序差)仅为50ps,这对于保持多个外围负载之间的同步至关重要。该缓冲器以一个微小的2×2mmDFN封装供货,这种小尺寸是许多先进的便携式应用非常需要的。5PB11xx同时也可以及较大的3.9×4.9mmSOIC封装供货,可用于以往的设计进行性能升级,或用于电路板空间不是很紧张的新项目设计。

当然,虽然工作在200MHz、性能经过大幅度改善的5PB11xx器件简化了设计挑战,但它并不能完全消除电路设计者的责任。在200MHz频率下,仍然要应用良好的设计规范,包括12至18英寸(30到45cm)长的缓冲器与负载之间最大电路板布线长度,采用PCB板上的平衡布线以降低噪声和接地回路影响等等,同时也需要遵循其它的标准高频设计准则。

一些设计师或许在下述两种缓冲器之间难以抉择:一种具有较低抖动,但有较高并难以承受的功耗;另一种具有低功耗,抖动指标却逊色不少。IDT公司的全新时钟缓冲器产品系列不需要再有这种折衷。除了封装和引脚与已有产品兼容外,它们也可以更小的封装提供,这意味着设计师不仅可以在新设计中采用该缓冲器,同时可以在已有设计中利用这些器件的优势。

抖动表征和测试

抖动是一个简短的术语,但却是一个拥有许多技术细节的复杂主题。不仅有许多类型的抖动,同时也有不同的度量方法来评估抖动,抖动类型和值的大小依照具体的应用而有不同的结果,欲了解更多信息,请参阅附表。两个信息量很大的参考文献是AN-815理解抖动单位和AN-827时钟抖动的应用关联。

在评估抖动时,重要的是设计师要针对多个抖动指标做“树状分析”,分析它们如何汇合在一起,确保抖动结果在一定范围内,并且抖动的系统级影响可以接受。同样重要的是对于那些计划实际测试并确认其抖动分析的工程师,必须要了解在当今设计中非常快的时钟和非常低的低抖动带来的挑战。在设计、安装、测试设备、计算等确认测量过程的每一个环节,都存在一些复杂而微妙的因素,有时侯很容易进行一些不当的测试,可在不经意间误导并生成一些数字,导致对结果的过于乐观或者过于悲观。

作为一家时钟发生器和缓冲器IC的领先厂商,IDT公司拥有针对这些测试的丰富经验,所有器件正在使用是德科技(KeysightTechnologies,以前的安捷伦)的E5502相位噪声测量解决方案等仪器进行测试,见图SB-1。该仪器经专门设计,可用于在设计评估和生产阶段测量非常低的相位噪声。它采用一个具有参照源技术的相位检测器来测量时钟或缓冲输出的单边带(SSB)相位噪声特性。该测试装置的设计不仅始于高精度信源,同时也采用一个独特结构,可以抵消掉许多内部错误,这些错误因而就不会影响到被测器件上的最终数据。

没有任何一个单一的数字可以简单地汇总所有应用中的抖动。哪些指标对于给定的设计是最相关的,并且这些是如何由时钟组件供应商测量得出,了解这些对于在特定情况下作出最佳选择非常关键。这将使设计人员在考虑设计优先性和制约性的情况下正确理解数据表的参数。