- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

经验分享:使用多个时钟时,如何改善系统性能?

在使用同一时钟源产生多个时钟时,一个常见的问题是噪声,通常表现为存在于噪底之上的杂散,这是因为单一时钟源被倍频或分频为多个时钟。偏移各时钟的相邻沿可以降低噪声杂散,或者完全消除杂散,这具体取决于系统的时序裕量。这一现象是一个时间变量系统,其中时钟信号的破坏与时域中的干扰位置相关。干扰位置是固定的,因此时钟的破坏程度与干扰的幅度成比例,就像在线性系统中一样。

来,送个例子,以时钟发生器AD9516的两路输出为例加以说明吧~

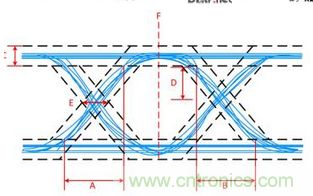

一路100MHz输出连接到一个ADC,另一路2 5 M H z 输出(1/4&TImes;fSAMPLE)为一个FPGA提供时钟信号。两路输出时钟的上升沿和下降沿几乎是同时的,其结果是发生耦合效应,因为两个快速运动的高带宽时钟沿每隔10ns出现一次,而不是所需要的一个时钟沿。在此跃迁期间,内部或外部的噪声必须很低,因为抖动或噪声存在于时钟的跃迁区时会破坏ADC的时序。提高压摆率以加快时钟沿(阈值区相应变小)不可避免地会缩短噪声在阈值期间存在的时间,从而有效降低引入系统的均方根抖动量。在时钟的稳态期间(高电平和低电平),时钟噪声不起作用。因此,只需延迟25MHz或100MHz时钟便能展开二者的时间,移动干扰的位置。换言之,应将一个时钟的跃迁沿安排在另一个时钟的稳态期间出现。

本质上,这里涉及到一条走线与另一条相邻走线由于串扰而引起的抖动(噪声)。如果一条走线携带一个信号,而相邻的并行走线携带一个变化电流,则信号走线中将产生一个电压;如果它是时钟信号,则时钟沿出现的时间将被调制。如果这些时钟沿出现在几乎同一时间,就会发生问题。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:作用大技巧多,一文看懂载波聚合那些事

下一篇:不知道5G?不知道5G优势?看这里!