- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字射频存储技术是什么,射频电源该如何接地?

射频电源应该如何接地?

在Vcc星型拓扑的主节点处最好放置一个大容量的电容器,如2.2μF。该电容具有较低的SRF,对于消除低频噪声、建立稳定的直流电压很有效。IC的每个电源引脚需要一个低容量的电容器(如10nF),用来滤除可能耦合到电源线上的高频噪声。对于那些为噪声敏感电路供电的电源引脚,可能需要外接两个旁路电容。例如:用一个10pF电容与一个10nF电容并联提供旁路,可以提供更宽频率范围的去耦,尽量消除噪声对电源电压的影响。每个电源引脚都需要认真检验,以确定需要多大的去耦电容以及实际电路在哪些频点容易受到噪声的干扰。

良好的电源去耦技术与严谨的PCB布局、Vcc引线(星型拓扑)相结合,能够为任何RF系统设计奠定稳固的基础。尽管实际设计中还会存在降低系统性能指标的其它因素,但是,拥有一个“无噪声”的电源是优化系统性能的基本要素。

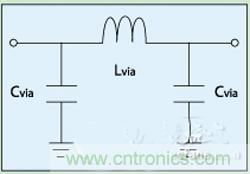

图3.过孔的电特性模型

接地和过孔设计

地层的布局和引线同样是WLAN电路板设计的关键,它们会直接影响到电路板的寄生参数,存在降低系统性能的隐患。RF电路设计中没有唯一的接地方案,设计中可以通过几个途径达到满意的性能指标。可以将地平面或引线分为模拟信号地和数字信号地,还可以隔离大电流或功耗较大的电路。根据以往WLAN评估板的设计经验,在四层板中使用单独的接地层可以获得较好的结果。凭借这些经验性的方法,用地层将RF部分与其它电路隔离开,可以避免信号间的交叉干扰。如上所述,电路板的第二层通常作为地平面,第一层用于放置元件和RF引线。

接地层确定后,将所有的信号地以最短的路径连接到地层非常关键,通常用过孔将顶层的地线连接到地层,需要注意的是,过孔呈现为感性。图3所示为过孔精确的电气特性模型,其中Lvia为过孔电感,Cvia为过孔PCB焊盘的寄生电容。如果采用这里所讨论的地线布局技术,可以忽略寄生电容。一个1.6mm深、孔径为0.2mm的过孔具有大约0.75nH的电感,在2.5GHz/5.0GHz WLAN波段的等效电抗大约为12Ω/24Ω。因此,一个接地过孔并不能够为RF信号提供真正的接地,对于高品质的电路板设计,应该在RF电路部分提供尽可能多的接地过孔,特别是对于通用的IC封装中的裸露接地焊盘。不良的接地还会在接收前端或功率放大器部分产生有害的辐射,降低增益和噪声系数指标。还需注意的是,接地焊盘的不良焊接会引发同样的问题。除此之外,功率放大器的功耗也需要多个连接地层的过孔。

图4.以MAX2827参考设计板为例的PLL滤波器元件布局

滤除其它级电路的噪声、抑制本地产生的噪声,从而消除级与级之间通过电源线的交叉干扰,这是Vcc去耦带来的好处。如果去耦电容使用了同一接地过孔,由于过孔与地之间的电感效应,这些连接点的过孔将会承载来自两个电源的全部RF干扰,不仅丧失了去耦电容的功能,而且还为系统中的级间噪声耦合提供了另外一条通路。

在本文的后面部分将会看到,PLL的实现在系统设计中总是面临巨大挑战,要想获得满意的杂散特性必须有良好的地线布局。目前,IC设计中将所有的PLL和VCO都集成到了芯片内部,大多数PLL都利用数字电流电荷泵输出通过一个环路滤波器控制VCO。通常,需要用二阶或三阶的RC环路滤波器滤除电荷泵的数字脉冲电流,得到模拟控制电压。靠近电荷泵输出的两个电容必须直接与电荷泵电路的地连接。这样,可以隔离地回路的脉冲电流通路,尽量减小LO中相应的杂散频率。第三个电容(对于三阶滤波器)应该直接与VCO的地层连接,以避免控制电压随数字电流浮动。如果违背这些原则,将会导致相当大的杂散成分。

数字射频存储技术是什么?

数字射频存储器(DRFM)是现代电子对抗系统中有源雷达干扰机的主要组成部分,用于将接收到的雷达信号精确地复制后再返回该雷达系统,以此来混淆该系统。正是应用DRFM的精确复制雷达信号的特点,DRFM技术已经广泛应用于各种雷达回波信号发生器、雷达综合测试仪和各类通用信号源的研制。为了更好地保真复制各类信号,为研究数字射频存储器提供可靠的仿真理论依据是本文的主要研究内容。

1.基本原理

数字射频存储(DRFM)的基本工作原理:首先将输入射频信号下变频为中频信号,经A/D变换后成为数字信号,写入高速存储器中。当需要重发这一信号时,在控制器控制下读出此数字信号并由D/A变换为模拟信号。然后用同一本振作上变频,得到射频输出信号,完成对输人信号的存储转发。

首先对量化过程进行分析,现假设基带输入信号为一个正弦信号gi(t)=Esinωit,量化位数为N,经过量化后的信号可用阶梯波y(t)表示,y(t)可以被认为是N对矩形波的叠加。如果A/D变换的量化位数为m,那么正或负半周的量化台阶数为N=2m-1。

阶梯波的表达式为:

E2n+1就是量化产生的谐波分量幅度,可由该式计算各阶谐波的功率。

在采样的过程中,为简便起见,以一位量化信号作为输入,则输入信号为:

式中:E,ωi分别为输入信号的幅度和角频率。设采样脉冲信号为fs(t),采样后的信号为fo(t),则采样过程在时域上的数学表示式为fo(t)=fi(t)fs(t),在DRFM中采用等间隔均匀采样,采样周期为Ts,采样时钟频率ωs=2πfs。在实际电路中,采样是在采样脉冲上升的瞬间完成的。因此采样脉冲的宽度可以看成一个窄脉宽,用τs。来表示。采样脉冲的傅里叶级数为:

式中:Es,τs,Ts和ωs分别为采样信号的幅度、脉宽、周期和角频率。则:

在式(6)中,第一项是基带的谐波信号,是由量化所产生的频谱成分,只有在基带滤波器内,谐波将成为寄生信号,所有nωi》ωs/2的项将被滤除(n取奇数);第二项则完全在滤波器外,不用考虑;第三项是交调信号,满足(mωs-nωi)《ωs/2的所有成分,将成为交调寄生信号,它们是信号谐波与时钟谐波的交叉调制引起的。若以D表示脉冲信号占空比,且忽略第二项,则式(6)变为:

式(8),式(9)即为计算1 b量化DRFM的高次谐波和交调信号幅度的方法。

2.仿真模型

通过建立数学模型,应用当前功能强大的Matlab中Simulink工具箱可以很好地实现该系统的仿真。采样与量化过程的仿真建模如图1所示。

信号发生部分采用Signal Generator模块产生正弦波;噪声源采用Gaussian Noise Generator,Zero-Order Hold模块实现采样功能。Compare To Zero模块实现单比特量化,Uniform. Encoder模块实现多比特量化。各路信号分别经Data Type Conversion转换为合适的数据格式,送入Spectrum Scope显示频谱。该模型同时显示四路信号经处理后的频谱,四路信号由同一信号源产生,以使得结果更具可比较性。为了尽量模拟实际环境,加入了均值为0、方差为0.01的高斯噪声。

3.仿真分析

(1)输入信号频率fi=10 MHz,经理论分析计算得到表1。

对模型进行仿真得到结果如图2所示((a)~(d)分别对应于仿真模型的四个支路)。

(2)输入信号频率fi=20 MHz。经理论分析计算得到表2;对模型进行仿真结得到结果如图3所示((a)~(d)分别对应于仿真模型的四个支路)。

由理论图表及仿真图形可知,该组仿真方案没有谐波产生,频谱图中仅有45 MHz处的基波和15 MHz,75 MHz处的交调,这一现象是由于信号频率过高,以致于谐波频率过高而被基带滤波器除去。尽管没有谐波产生,但是交调的功率很大,对系统的高性能工作同样是一个不利因素。

4.结语

综上所述,根据采样与量化过程仿真分析可以得出:

(1)采样和量化使信号频谱发生变化,出现了新的频率分量——谐波和交调,降低了DRFM的有效发射功率,使得系统的工作能力变差。

(2)噪声污染会使频谱变得更加复杂,对于一个系统,输出信噪比取决于输入信噪比和系统内部信噪比,因此噪声的存在必将降低DRFM的信噪比。

(3)总的来讲,谐波分量随频率增加降低,而交调分量随频率增加升高,也就是说高次谐波幅度较低次的小,而高次交调幅度较低次的大。

(4)当信号频率和采样率一定时,提高采样率或增加量化位数都可以起到抑制寄生信号的作用。具体来讲,提高采样率对交调有很好的抑制作用,而对谐波作用不明显;增加量化位数对交调和谐波都有很好抑制作用。