pll的杂散(毛刺,边带)

check power's spectum

PFD的构造也有关,是否先对参考频率除以2了?

这个是怎么跑出来的啊?似乎不像pss+pnoise跑出来的

难道是fft?

您好,没看明白你的意思,望详细指导。

Pfd 就是普通的门电路Pfd ,没有对输入频率进行处理(除2)啊。不知道是哪里来的6M的纹波。

不是的。

pss+pnoise也能够跑功率谱密度分析?

我也好奇那图怎么跑出来的?测试的?

对输出波形做FFT吗?

看错了,还以为你用pss+pnoise跑pll。

对输出做PSD

可以考虑看看VCO control line上面spur是怎么样的,可能有fref/2的干扰

你好,控制电压上没有6M的波动,只有12M的周期波动。唉,哪的问题呢。

确实挺奇怪的,我觉得可能是VCO 的结构有问题吧。可以考虑把VCO开环单独测试,给一个DC+12MHz的干扰,看看输出频谱。

有意思的是几个月前,另一个group也在讨论这个问题。http://www.linkedin.com/groupItem?view=&srchtype=discussedNews&gid=27032&item=85110533&type=member&trk=eml-anet_dig-b_pd-ttl-cn&ut=2CWqMaRiC3D5c1。

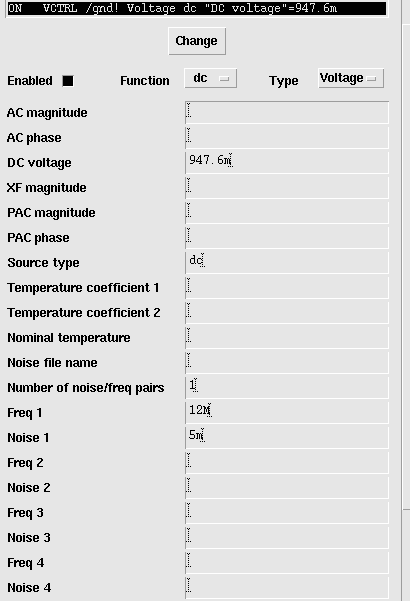

你好,这个干扰信号该怎么加?没用过,请指教!是图中的“noise/freq pairs”吗?freq1和noise1各代表什么呢?

怀疑你这是FFT导致的——240MHz及其谐波与FFT的sample频率之间相互混叠。

FFT的sample频率是多少?

另一个话题:你不应该对vco输出做频谱分析来看pll的性能——impossible

你可以对vctrl做频率分析,因为它是带限的且信号频率很低,fft能看到准确的频谱信息。

vco输出不仅频率高而且不带限,fft的结果包含了频谱泄漏和频谱混叠,是不真实的。

想知道pll的噪声性能,你应该用noise的线性model

小数pll中对sdm这部分的噪声你倒是可以用时域model——不过也没啥意义。

不认同17楼的意见

大家一般对PLL的噪声特性进行分析不就是用安捷伦的设备对PLL输出进行FFT分析么,那个功率谱的特性就是FFT的结果么,而且最终包含各种部分噪声贡献的信息也只有在PLL输出能够看出来。

至于说到频谱泄露,加窗函数能够解决的问题。

说到混叠,我认为那个6M的信号肯定不是混叠的结果。

别误导~ PLL测试需要确定输出频谱~真心想不通干嘛要看vctrl的

是很诡异~已知理论上不应该出现6MHz的谐波~你要不用Hspice再跑一个Trans~ex里转了数据文件重新fft看看~确定一下这个是电路问题还是仿真软件的问题~

同意~肯定不是混叠~混叠混不出1/2来~

mark。

怎么做PSD啊,求指教

高端大气上档次

以前做PLL都不看相位噪声

直接看抖动

应该是一样的

您没,不知道您这个问题解决了吗,我最近也遇到相同的问题呢.

小编 能介绍一下你的仿真方法和设置吗!?多谢多谢!

mark一下,学到了很多东西,希望大家帮忙解决下这个问题。另外,怎么仿真出来频谱啊?哪位前辈有比较详尽的PLL仿真方法,包括pss+pnoise和频谱分析等等。

小编,能做个文档介绍下你的仿真设置吗?

你这个纹波好小啊!能不能说下你的环路滤波器的电容大概多大?

你确定取的时间窗长度对吗?通常情况下电路级的VCO的fft肯定有问题的,但是如果verilogA模型就可以,因为输出的频率是定的,所以整数倍的VCO的周期的时间长度就ok,fft肯定能看出来的。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。