pmos电流镜问题

录入:edatop.com 阅读:

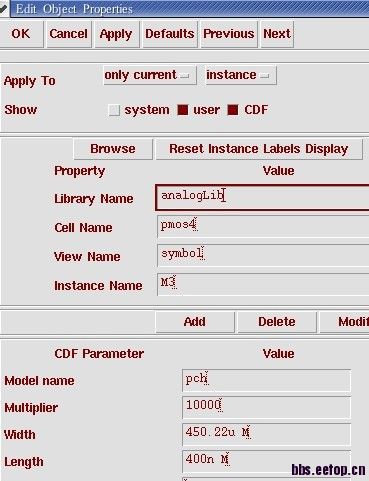

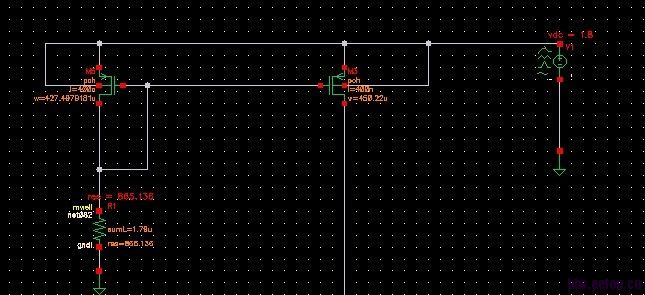

设计一个2mA的pmos电流镜时。电流镜中的偏置管M3的D级已知为1.4V左右,假设它的G级电压为1.5v,而S级与衬底都是1.8V的话,在cadence中设置M3的沟道长度为400nm,宽度为变量,仿真出来的电流与宽度的关系曲线时,电流只有nA数量级。然而把管子的Multiplier要改为10000时,才会让MOS管的Id为mA的数量级。

最后仿真出来要获得2mA的电流,M3的尺寸为下图所示。为什么pmos管的电流会这么小?要这么大的管子来实现?[img]file:///D:/Program%20Files/Tencent/QQ/Users/476200320/Image/(`W$JDKGM3PD10Y1E6}G@[6.jpg[/img]

最后仿真出来要获得2mA的电流,M3的尺寸为下图所示。为什么pmos管的电流会这么小?要这么大的管子来实现?[img]file:///D:/Program%20Files/Tencent/QQ/Users/476200320/Image/(`W$JDKGM3PD10Y1E6}G@[6.jpg[/img]

补发图片下,

无语...vsg=0.3v,你的p管导通了么?

哦,是这样啊

汗一个!

M3的栅压1.5,而S端电压为1.8,那么Vgs就太小了,M3在亚阈值区工作了。可以降低阻抗值来使得M3的栅压变得更低一些,使M3开启。

great support

rencai

要先看 print operation point里面的工作区域阿

是的。呵呵pMOS迁移率本来就低,当然要很大的宽W.我也是菜鸟,学习了

thanks

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:低功耗DCDC设计

下一篇:smic工艺库没有小电阻的mismatch怎么做电阻串