全差分输出运发测压摆率

录入:edatop.com 阅读:

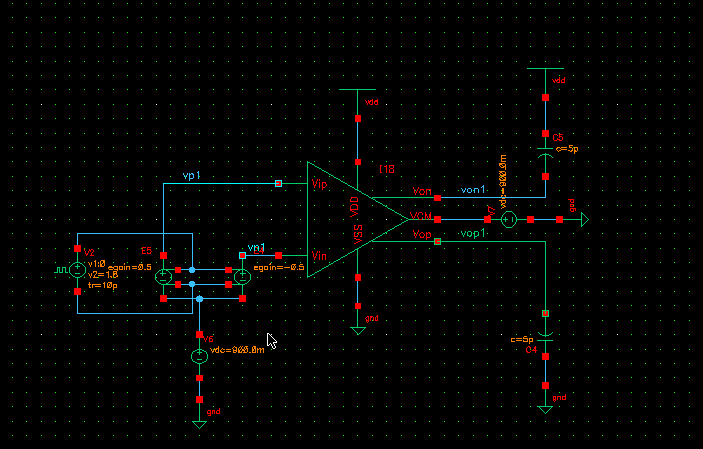

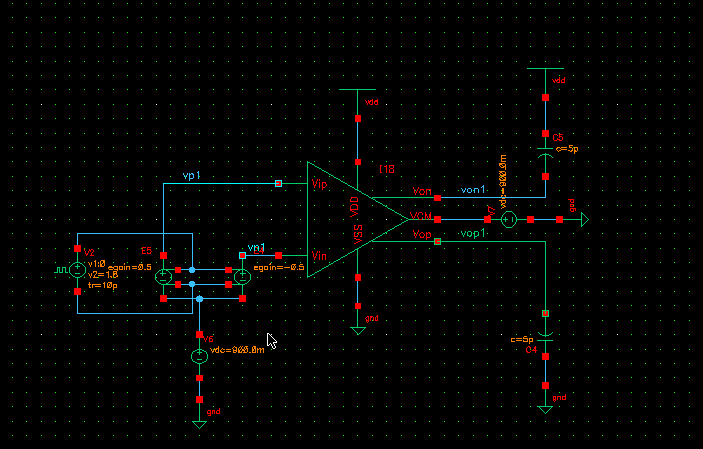

各位大神好,最近在做全差分运放的仿真,我用如下图所示的测试平台测量出的压摆率很不对。好像是一直都没建立完成,

是我的测试平台搭建的有问题还是其他的问题呢,?请大神们不吝赐教

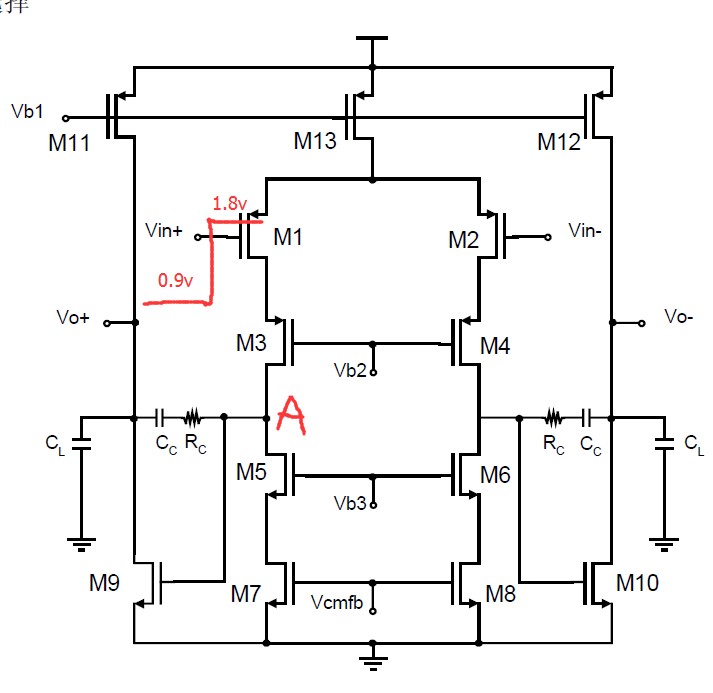

电路结构我是参照唐长文老师的报告里搭建的

(1) (2)

(1) (2)

是我的测试平台搭建的有问题还是其他的问题呢,?请大神们不吝赐教

电路结构我是参照唐长文老师的报告里搭建的

自己顶一下

(1) (2)

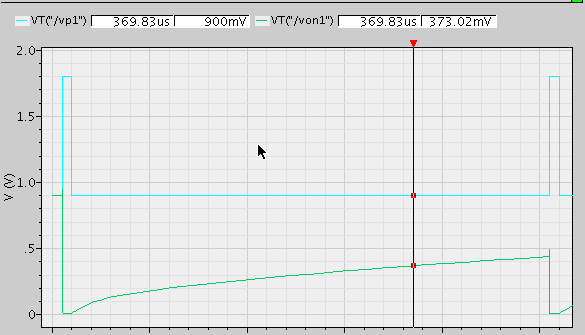

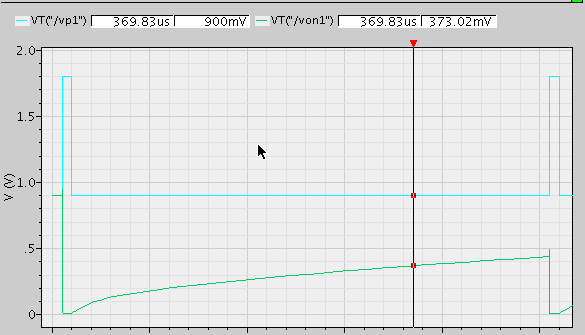

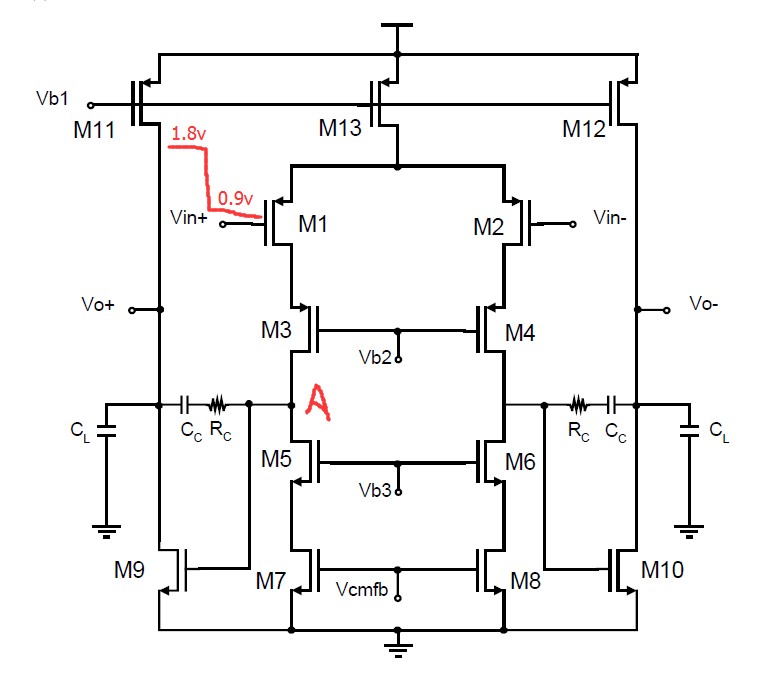

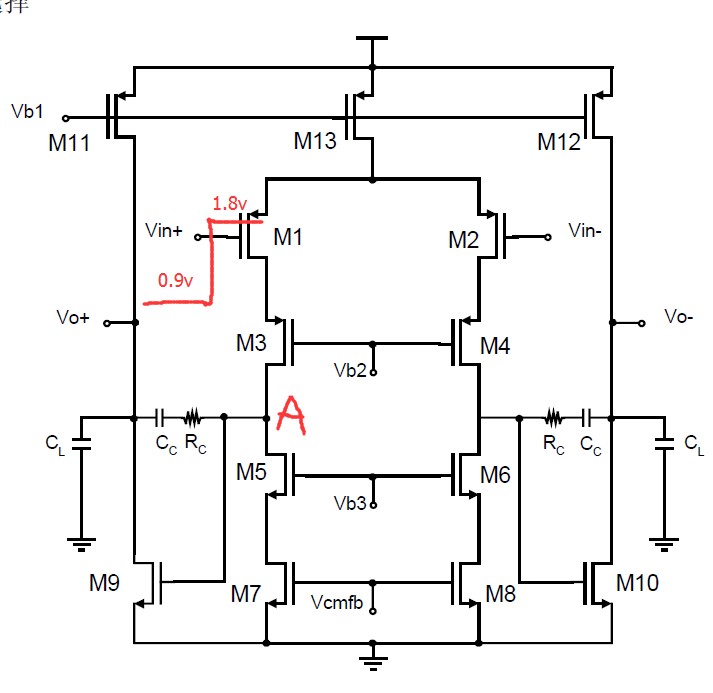

(1) (2)如图1所示,从Vin+输入阶跃信号(1.8v到0.9v)其中0.9v是共模电压,同理从Vin-输入相反的阶跃信号(0.9v到1.8v)。当Vin+为1.8v时M1处在截至区,M2处在线性区。A点电压很低,使得M9也处在截至区,Vo+输出约为1.8V。当Vin+跳变到0.9V时,M1处在饱和区,为A点充电,A点电压升高。当A点电压上升到一定值时使M9处在饱和区,同时Vo+下降到约为0.9V。

但是,我在仿真这种结构运放的压摆率时,输入了如上图所示的阶跃信号,当Vin+为0.9V时,A点电压在瞬间上升到一个值后上升的非常缓慢,使得Vo+的电压下降的非常缓慢(10us内Vo+的值只下降了几十毫伏),Vo-的情况跟Vo+一样。

当我将输入阶跃信号Vin+改为从0.9v到1.8v(如图2所示)时,A点电压瞬间变小,Vo+也瞬间从0.9v变到1.8V。

这个问题我找了好长时间,还是没有解决,请问大神们在仿真全差分输出运放的压摆率时遇到这种现在了吗?请大神们不吝赐教。小白感激不尽!

哪位大神可以帮帮忙吗?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。