关于delta-sigma 调制后接 滤波器的问题

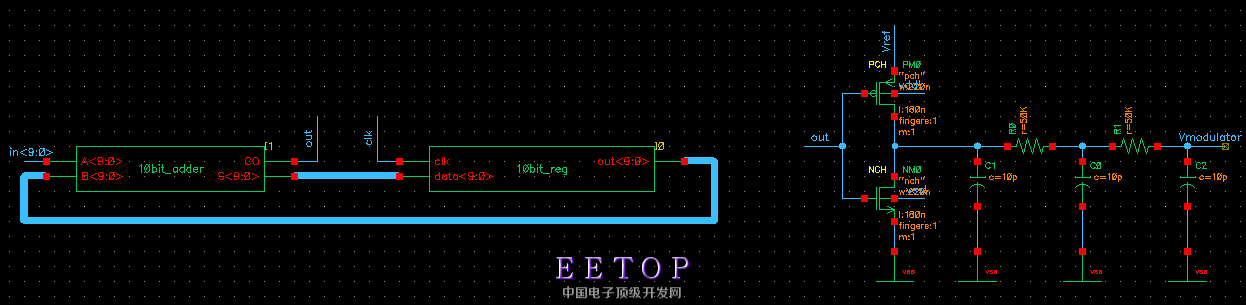

电路贴了图,有点像 DAC 的感觉,但是这边数字控制字是一定时间内不变的,不知道滤波器的截至频率该由什么确定?(delta-sigma DAC 中是得<0.5fin吧)

是和dac 差不多意思。

设在quantizaiton noise << thermal noise 的点。

不好意思,还是有点不大清楚。具体到图里的电路中,该怎么做?

用个RC 滤波器放在基准输出。

是的,我也是这么做的(图上已画出)。因为delta-sigma是一阶的,我用了两阶的RC来滤波,滤波器的-3dB约等于 0.5倍的调制器时钟频率,不知道这种做法是否正确?

还有,这样做出来输出端还是有明显的纹波,我又加了一阶RC且用大电容后挺平滑了,加了这些后有个问题:输出基准值还能和理论上结果相同吗(理论上 应该符合 控制字 与 2^n 的比例关系吧)?

你好像要找些sigma-delta dac 的资料来看看。 把rc filter 的频率设在高速时钟附近,基本上没啥用。 3db 带宽够低的话,一阶filter 也够用。你可以看输出的fft

输出平均值和你的控制代码肯定能对上。要不电路就做错了

OK,多谢你的回复,实在是帮了大忙

滤波器的截至频率由系统的过采样率OSR决定。即截止频率 wc=fin/OSR。

另外要效果好,最好提高阶数。

你好,我这里外部给的控制字几乎是固定的、静态的(只在需要调节的时候改变一下控制字),不知道这个 OSR 该如何衡量?(OSC是指 采样频率比信号带宽 吧,这个好像没有 信号带宽 的概念?难道是DC?)

另外,感谢你的回答,直接说到我想问什么。

你这个是做 ad的思路。 dac 一般不这么搞

OSR是采样频率与信号最高频率的比值。如果高频时钟不能动,那对你来说OSR就是一个不可调整的常量了。

如果你对控制字变化的瞬态不关心的话,可以认为输入是DC。

因为是一阶调制,DC输入通常会引入量化噪声引起的谐波。

DC是最好加上高频jitter,以避免量化谐波。或者用高阶的调制。

AD与DA都一样。只是小编没有定义他的指标与约束条件。

OSR好像是采样频率与2倍带宽的比值。

不都约束了么?基准输出。为了直流调整精度。

sigma-delta ad 和 da 的滤波哪能一样? 一个是数字滤波器,一个是模拟滤波器。玩法不一样。

是的。OSR应是采样频率与2倍带宽的比值。

我指的约束是指基准输出要求的精度或等效比特位,及可以使用的芯片面积或成本等。

低成本与高指标有不同做法。

另外我说的AD与DA都一样是指sigma-delta 调制器部分,不是滤波器部分。可能是我没有说清楚。

AD/DA中的sigma-delta 调制器的阶数提高都可以提高系统的有效比特。

如果直流调整精度要求高,而且小编的OSR已经固定了,那就可以增加sigma-delta 调制器的阶数来提高直流调整精度。

由于一阶调制器的量化噪声不是白色的,所以输出会有一些谐波出现。通常效果不会太好。如果系统指标已经达到了,那当然也无所谓了。

thanks

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:cadence SpectreVerilog 仿真数字部分延时问题

下一篇:关于TSMC 0.18um 的隧穿仿真