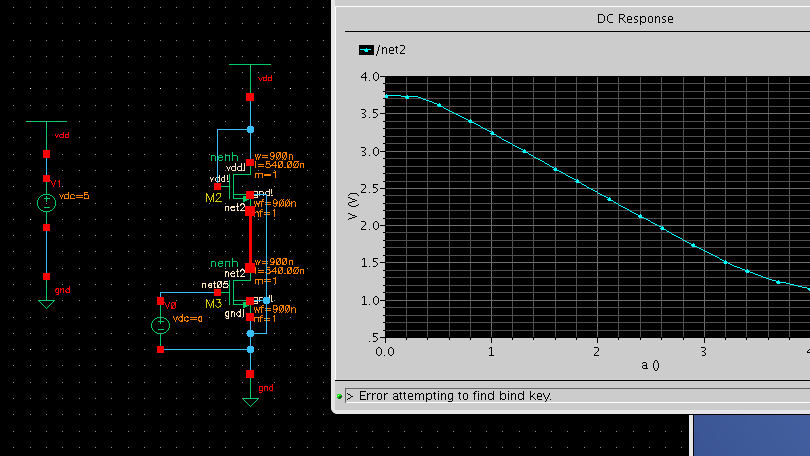

二极管连接的负载的共源极仿真问题

录入:edatop.com 阅读:

我是在看拉扎维的书时发现的问题,上图就是二极管连接的负载共源极单级放大器,图中我标红的线就是仿真图里的曲线,电源是5V,输入我用dc扫描,从0V到5V,拉扎维书里说如果输入小于阀值电压的话,输出应该是vdd-Vt。但我输入等于0V时仿真出来的结果却是小于vdd-Vt,还有按我自己的理解0V时下面的输入管不是应该不导通吗,输入应该被拉到电源电压的吗,但实际为什么是低于vdd-Vt那么多?

:'(:'(:'(:'(

MOS管在截止的时候也是有漏电的,大约有-10量级的电流,因此可以把它看成是个极大的电阻。而上面那个饱和区的MOS管的电阻也很大,只是比截止区MOS管的电阻小几个量级,因此VOUT实际上是两个电阻的分压,比较接近VDD的电压。

为什么小编觉得不是Vdd-Vt呢?考虑到衬偏的存在,Vt到1.2V完全有可能啊!

建议作diode的NMOS用PMOS代替。

there is a leakage current at the cutoff .. simulations are not 100% similar to equations

因为我以为管子截止时是没有泄露电流的,以为仿真是理想的

恩,是的,谢谢啦

把体端连接到源端上来消除体效应,再次仿真看看

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:MMSIM14,在redhat5下,集成到IC514报licence错误,但IC616不报错,求助大神

下一篇:新手求问关于tsmc 18rf电感版图问题