PLL相位噪声测试问题

录入:edatop.com 阅读:

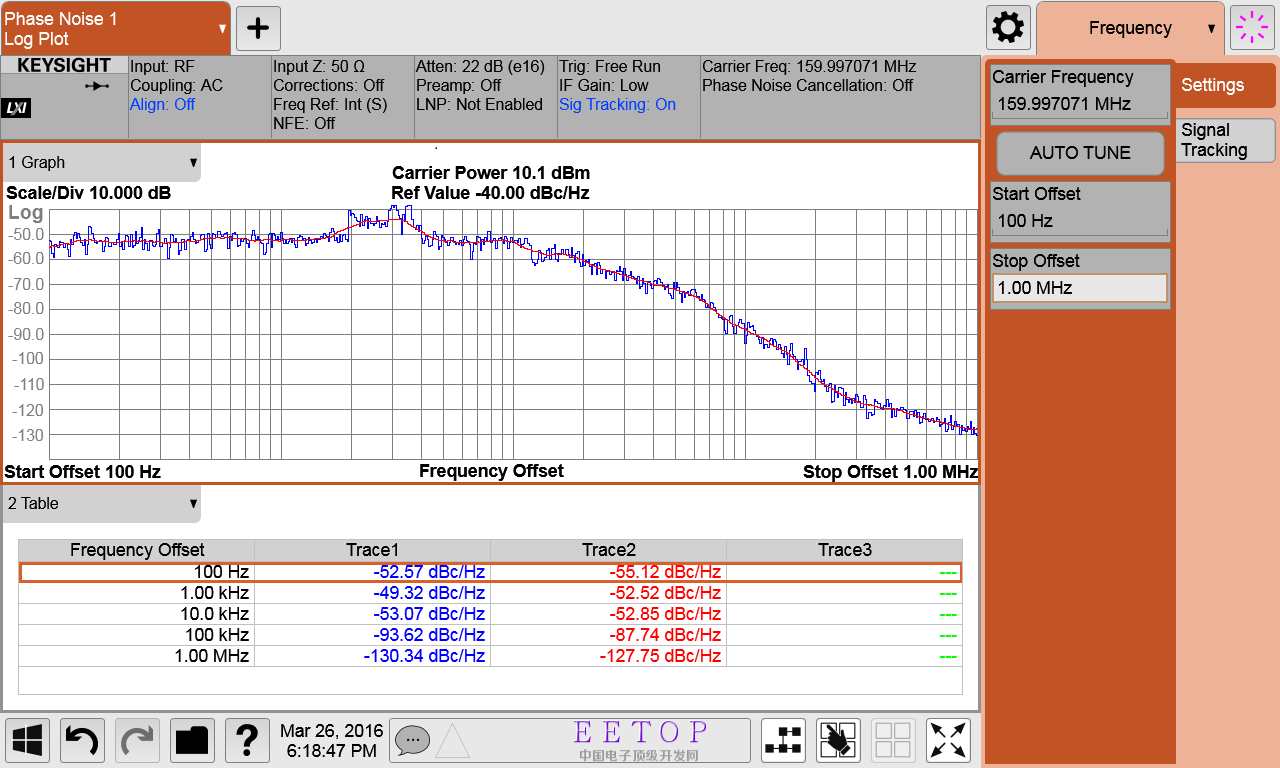

请教下,看一般的文献,载波功率都是负值的,我这个测试过程载波功率达到10.1dbm,可能存在的问题在哪里?

请教下,看一般的文献,载波功率都是负值的,我这个测试过程载波功率达到10.1dbm,可能存在的问题在哪里?求助求助?

10.1dbm,好大啊,怎么做的?我们做的PLL(做的很渣)也就负的十几dbm。是不是你们输出摆幅就是很大啊?你用示波器看看

猜测一下原因:

1. 频率低,容易推出大功率;

2. 驱动放大器电压高(现在发paper的都是一些先进工艺,电压本来就低,驱动能力除非专门做是不会很高的);

3. paper上不太关心底噪(测试时的高功率有助于测量底噪,但是现在大都是宽带调制,对底噪要求没那么高,也就不推很高的功率来测试了);

效习效习

用的哪种VCO呀,这个VCO的phase noise drop很快呀,带外40dbc/10倍频?表示很疑问呀....环路滤波器带宽多少?

是的,我在信号的输出添加了好些反相器级联构成的BUFFER,输出信号幅度很大。

就是我在信号的输出添加了好些反相器级联构成的BUFFER,会不会因为这个原因?请教下?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:管子 阈值电压的问题

下一篇:DC中怎么设置下降沿触发 输入延迟问题