请教Pipelined ADC的REFT,REFB buffer的设计

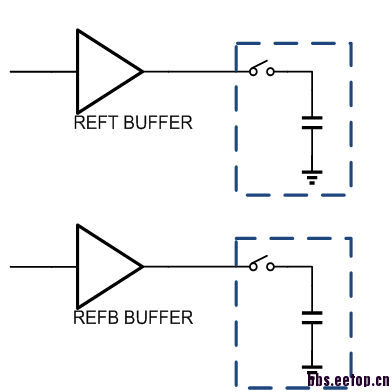

在pipelind ADC中,MDAC的开关电容需要有REFT和REFB电平,负载的开关电容切换会使得buffer输出端产生跳变,这时候要求两个buffer能够快速回复到所需电平,也就是建立时间要足够小,如果在上GHz的工作频率下这个建立时间可能就是几百ps。

那对于高速应用,这两个buffer的指标是否要满足带宽也要上GHz,什么样的结构合适呢?

如果在buffer输出端接一个大电容(ex. 100pF)来滤掉开关电容产生的波动是否现实,这是否又会引入一个问题:buffer的带宽会降到很低?

希望各位大神多给点指导意见,多谢哈!

DING YI XIA ,

还有,想问一下,在buffer后接一个大电容稳定电压,但是buffer的相位裕度是怎样处理的,

还是要求相位裕度要>60吗?

s & h !

xvvxcvxcvcxvcxv

I once designed a 8 bit 30MHZ pipeline adc, the reference buffer is integrated, so I just use 2 such kinds of buffer to get them. Between the VREFP and VREFN I gave a 10pF caps, which make the delta between VREFP and VREFN is the same when the switch on/off. The testing results OK.

For high resolution and high speed , I think there is a trade between the buffer response time and the output capacitance. Large capacitance will make the switching on/off impact decreasing but the buffer BW will decrease too.

you added a large capacitor, which is useful but you need added a large off chip capacitor and added 2 pins.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请问TSMC035工艺蒙特卡罗报错是什么原因啊?

下一篇:MOS管的驱动