请问如何设计一个LDO的shutdown电路

录入:edatop.com 阅读:

如果LDO是24V input, 5V output的话,enable pin=5V/0V,如何能够将这个LDO彻底关掉。

也可以是这样,此结构缺点就是工作电流大。可以考虑功率管换成nldmos,配合charge pump。

诚聘:实习生,电源管理 或 模拟 IC设计方向,沪上在读硕士生优先。

待遇:(40小时/周) 3000RMB/月,或 (30小时/周) 2500RMB/月。

工作场所不限,有意联系 leehying@163.com

另外友情提醒LZ:

即使是最小尺寸的高压MOS面积,也往往能够跟500/1的电阻面积抗衡

不用的时候,数字给enable信号不就行了?

你好,这个高压电路里MOS管的栅源电压没办法承受高压,是5g24d的mos管,因此不能按照通常的shutdown做法。

你可以用一个level shift将过来的数字信号给升起来嘛。

然后呢?控制管的栅源电压不还是可能承受高压吗

vgd有限制吗

那请问你24V电路怎么实现的?它都能承受高压,说明是可以用高压管子的,在通路上加一个相同类型的使能管难道就不能关闭?你还是上电路图吧,问题描述本来就含糊不清。

没有的

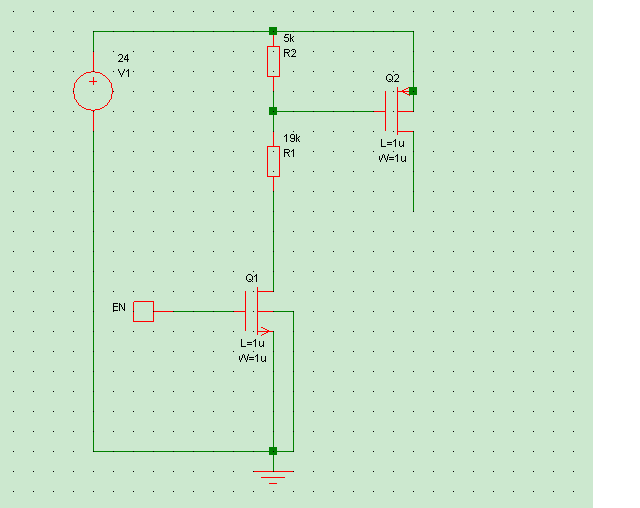

pmos做开关,用nmos下拉一串电阻分压输出作为pmos栅极开关,比如输入5Vnmos打开分压输出为24*(19/24)=19,输入0Vnmos关输出为24,那么p管vgs始终保持<5

非常感谢你的帮助,你的意思是这样的吧

這方法用的電阻小時真浪費電流24v/24k=1mA, 用大電阻24V/24M=1u卻浪費面積

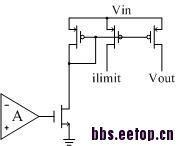

也可以是这样,此结构缺点就是工作电流大。可以考虑功率管换成nldmos,配合charge pump。

诚聘:实习生,电源管理 或 模拟 IC设计方向,沪上在读硕士生优先。

待遇:(40小时/周) 3000RMB/月,或 (30小时/周) 2500RMB/月。

工作场所不限,有意联系 leehying@163.com

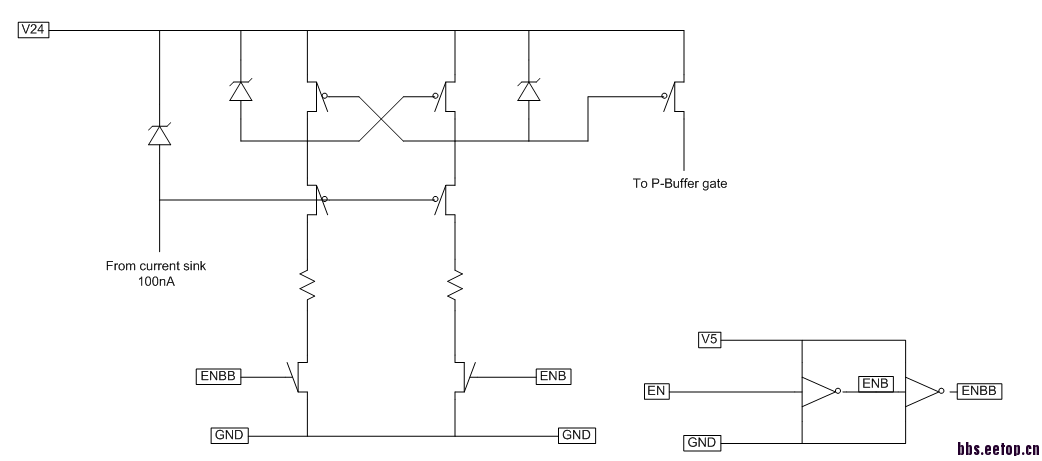

看来LZ想要小面积+低功耗,免费帮LZ设计一个

另外友情提醒LZ:

即使是最小尺寸的高压MOS面积,也往往能够跟500/1的电阻面积抗衡

很好。

是的,其他人说的方案都有可靠性问题

可以解释一下这个电路怎么工作的吗?

请各路大神支招

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:ADS2013

下一篇:对称性运放的失调电压应该怎么计算?