请教大家DFT/FFT的问题

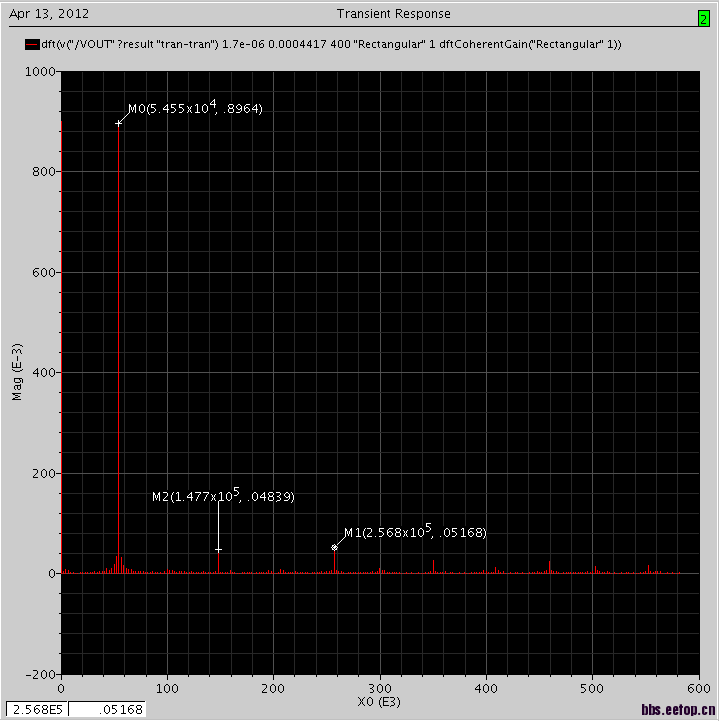

最近按一paper上描述搭了一个10位的SAR ADC,对输出做DFT如上图,如何得到SFDR/SNDR等参数?

还有,如果将输出固定间隔取2048个点导出来做fft的话,我对输入信号的采样次数需要大于2048么?还是可以不需要这么多采样次数仍按固定间隔取2048个点即可?

如果仿真时间过长,可能是什么原因造成的?电路全部管子搭成,无代码描述。采样频率1M,输入信号54.46M。跑30个信号周期就跑了一天一夜。

请教下大家

dB = 20log(Mag),用计算器就行了

ADC仿真时间长正常,曾经做一个12bit ADC仿DNL/INL花了8天8夜。想省时间选择性保存node,Cadence加个Turbo也能快不少

再请教个问题,如果将输出固定间隔取2048个点导出来做fft的话,我对输入信号的采样次数需要大于2048么?还是可以不需要这么多采样次数仍按固定间隔取2048个点即可?

10bit仿真取1024个点就够了

可能是我表达不清楚,这个我意思是对信号实际采样需要1024次还是可以少于1024次采样但是取1024个点就可以。就是在一次采样中取多个点分析是否是有效的。谢谢。

你这个结果不是很好,似乎才26dB

2次3次谐波太高了

真费解啊

不需要这么多点

尤其是最初debug期间,64 point dft也能看出问题来

仿真时间和保存多少node并没有关系吧,难道你验证过了?

存到少node只是最后你的瞬态结果的文件大小不同,一般来说存全部结果,会爆掉的,因为数据量太大

但是这个和仿真快慢没有关系,因为不管你存不存所有节点,在每个step上,所有节点的值都是要被计算出来的,

只是最后有多少数据写到data file中罢了

BTW:simulation 做DNL/INL 也比较困难,只能加 ramp波形,而不是我们测试中的码密度测试

只是看了个paper随时搭的。跑了一天一夜数据量是很大。性能是很差,呵呵。请问如何设置选择性保存node?

是不是表达不清楚

还真试过,会快不少

64个point太少了吧,noise floor太高,有时一些问题会被掩盖掉.

lz那个估计是单端SAR

差分的啊。

还有关于采样次数和取点的问题?谢谢

保存所需要的节点,ADE 界面

output-> save all -> selected

然后 to be plotted -> select on schematic , 电路上选所需要的点

感觉你的频谱有泄漏,需要非相干采样,输入信号频率要根据采样频率来算一下,并不是随意给的

真怀疑这个结论,

我也怀疑,平时也存过点多点的情况,感觉不到

与其怀疑不如试试,以前做PLL和ADC一开始都不是选择性保存,仿真时间都相对很长

关于取点的问题,一般是建议取2^(n-1)个点,也就是说,对于仿真而言,10bit取512个点是合适的。至于小编的问题,采样次数=取点数,要512个点,你就采样512次

多谢!

我是按照Fin/M=Fs/N计算的输入信号频率。

那可能是应为你data存不下了,或者仿真读写data出问题了

一般我存所有点的仿真都是爆掉的

我存一点的仿真和存几十个点的仿真感觉不到差别,都是一晚上

Fin/M=Fs/N 可以,但要保证频谱不泄露需要最后一个采样点相对第一个采样点在整周期上。这个如果自己仿真可以做到,要是实际测试要考虑一些非整数频率,就不现实了,还是要加Kaiser窗后再来DFT/FFT才行。

还真试过,除非写暴硬盘,否则区别不大。

wocaishidac说的也没有错。如果硬盘速度是瓶颈的话,减少存的节点是可以减少仿真时间。不过如果你只是从几十个点减少到几个点,意义不大。

我指的是很大的系统及仿真,如果你只是做个opamp,全部存和部分存点当然没有区别。不信你拿个系统级的电路仿真试试,这个尤其在后仿上差别很大。当然我这个只是经验性的观察,没有理论依据,不排除楼上说的硬盘瓶颈问题

我是跑整个ADC的tran,存几个点和几十个点是差不多的

sampler nuber, sim time

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:传递函数 波特图的关系

下一篇:芯片反向设计电路整理和分析要怎么做