带隙基准电路仿真问题,为什么电路不能稳定工作

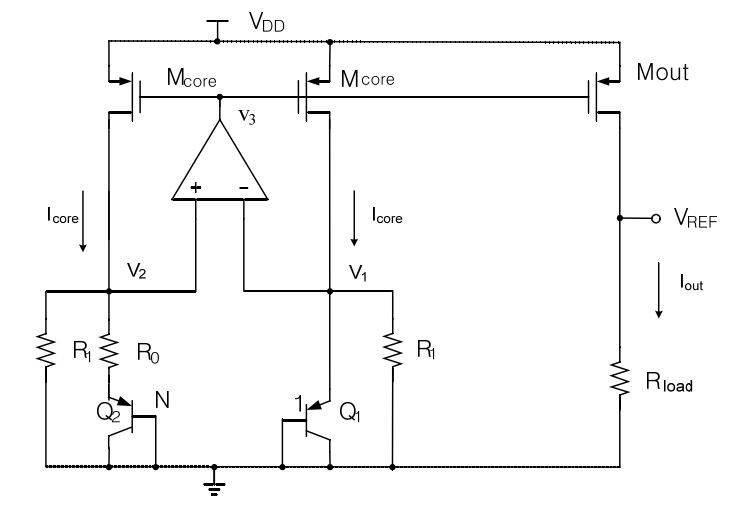

所用原理图是一个简单的带隙基准,如图

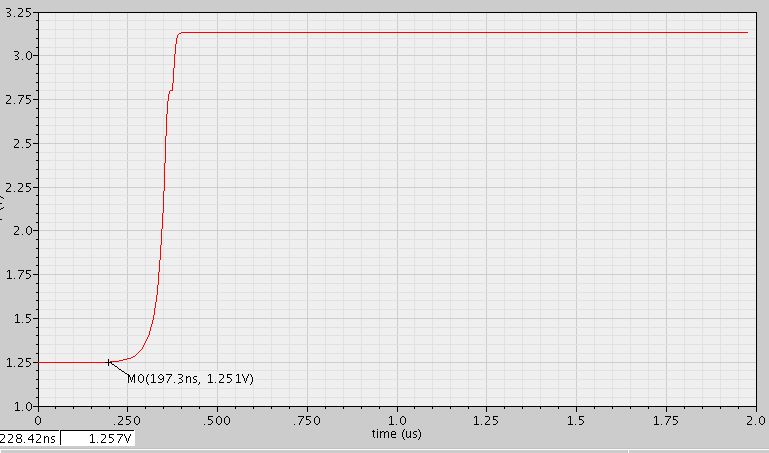

直流扫描的结果还是可以的,16PPM/℃,但是瞬态仿一下(使用Vdc),在2uS时间内,电压值从带隙输出的1.25突变为3.13,接近电源电压3.3,如图

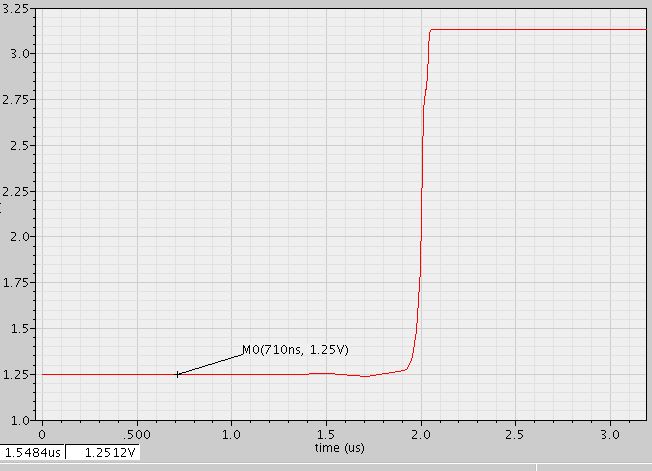

换了一个电源(0到10us电压3.3恒定的Vpwl),再仿瞬态,结果与上一次差不多,只不过突变时间变了。

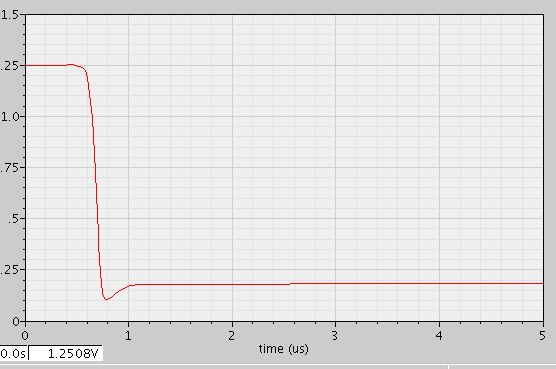

如果仿真时间改为5u,会出现下面的结果

请问这是什么原因引起的,是我的仿真不对吗还是电路有问题,我的电路里没有启动电路,因为我觉得他自己已经启动了啊,上电就是1.25,只不过后面不工作了,这个是启动的问题吗?

可能是不稳定。你的运放是一阶还是二阶?如果是后者需要电容补偿

运放就是一个差分放大器,只有一级,没加共源的第二级,不过带宽略小,4KHz左右。

看下运放的状态,再看看电路的环路稳定性吧

仿真1ms试试?

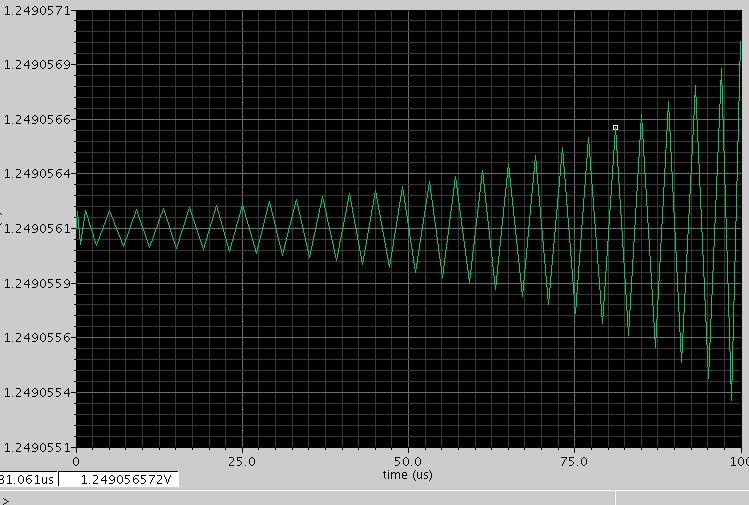

你好 感谢你的回复,用你说的方法试了一下。仿真时间在200us到20ms这个时间范围内,仿真结果都是稳定的,是1.25的直线,在50us到100us之间出现了下面的情况,有震荡但是还是在1.25附近

然后在10us和50us 之间,都是从1.25向0方向跳变。在5us以下都是向3.3方向跳变。

请问 这个原因到底是什么啊 仿真步长和精度对这个有什么影响 多谢

V3节点加个对电源的电容 尝试1p~5p的范围,看看是否会稳定

环路稳定性有问题。

1. bandgap need start up ..

2. sim 會和 sim step 有關..會 ring 一定是 迴授出問題 先看是PM

或如前說加 cap

sim time 拉長時有些 spice tool 會自動 step 取大點好跑快點, 但實際 CHIP 會不會RING 還很難說

因為 BANDGAP 有碰過SIM OK 但沒STAR UP

後來發現是RC DELAY 使某些CORNER會有問題

量產就是 YIELD LOSS ..

OPA bandgap 因為一般來說OP GAIN 很高, 只要一點NOISE OP就會比較 ,

所以 不給START UP 還是會動但是 就是

有風險

你的問題 LAYOUT後說不定會RC DELAY後就沒看到

但是 比較好設計是分析 Phase margin

另外也別排除是 spice tool 本身 not convergence ..

和spice tool 有關

andy2000a来自台湾吗,语言跟大陆的还是有些差别,有些理解不了。

Anyway, 不用STARTUP Circuit,对电源进行上电Tran仿真,确实也能够work,可能会有振荡,跟小编的情况类似,

但是不用STARTUP Circuit,真的可行吗?因没有做过相关的TAPEOUT,所以我对这个问题比较怀疑,请大牛指点

R1 R0 Icore,这几个参数你想设计到多少?

你给那个震荡图,电压幅度太小,不确定是否是真的震荡

不过7楼说的补偿方式是对的

为什么不加上start up呢?

也许反馈接错了,接成正反馈就到电源去了

把opamp输入极性反一下

Single stage not sufficient.Use two stage and compensate properly. Estimate node cap at v3 node and place 0.2*Cap_V3_NODE as miller cap for your opamp. Do not try to make excessively low power(Very high R1: this will cause another pole). Post sim results with these changes.

0.2*Cap_V3_NODE的是如何估算的啊?

他说的0.2*V3的电容,也就是2级放大器的Miller补偿的选取,把V3的电容当做2级放大器的负载,保证把次主极点推到3GBW之外,使整个环路稳定

上面的电流镜管构成共源第二级的,需要频率补偿的

闭环的接法没问题,这种结构本来就是正负反馈都存在,负反馈大于正反馈寻求稳定,但关键两点:

1.AMP的开环稳定是否OK?

2.闭环中R的设置,如果R设置不恰当,会造成负反馈和正反馈很接近,很容易不稳定

在v1、v2小于vbe时,左边电阻阻抗与右边阻抗相等,上面是PMOS电流镜,这样的接法形成的反馈,由于mismatch,可能是正反馈,也可能是负反馈,这该怎么解决?

恩兄弟你这问题解决没? 我用仿真130 smic 仿真时碰到了你同样的问题

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:CP的mismatch对phase noise的影响,求解

下一篇:求详细介绍Phase Noise的来龙去脉的书籍或者资料,越详细越好