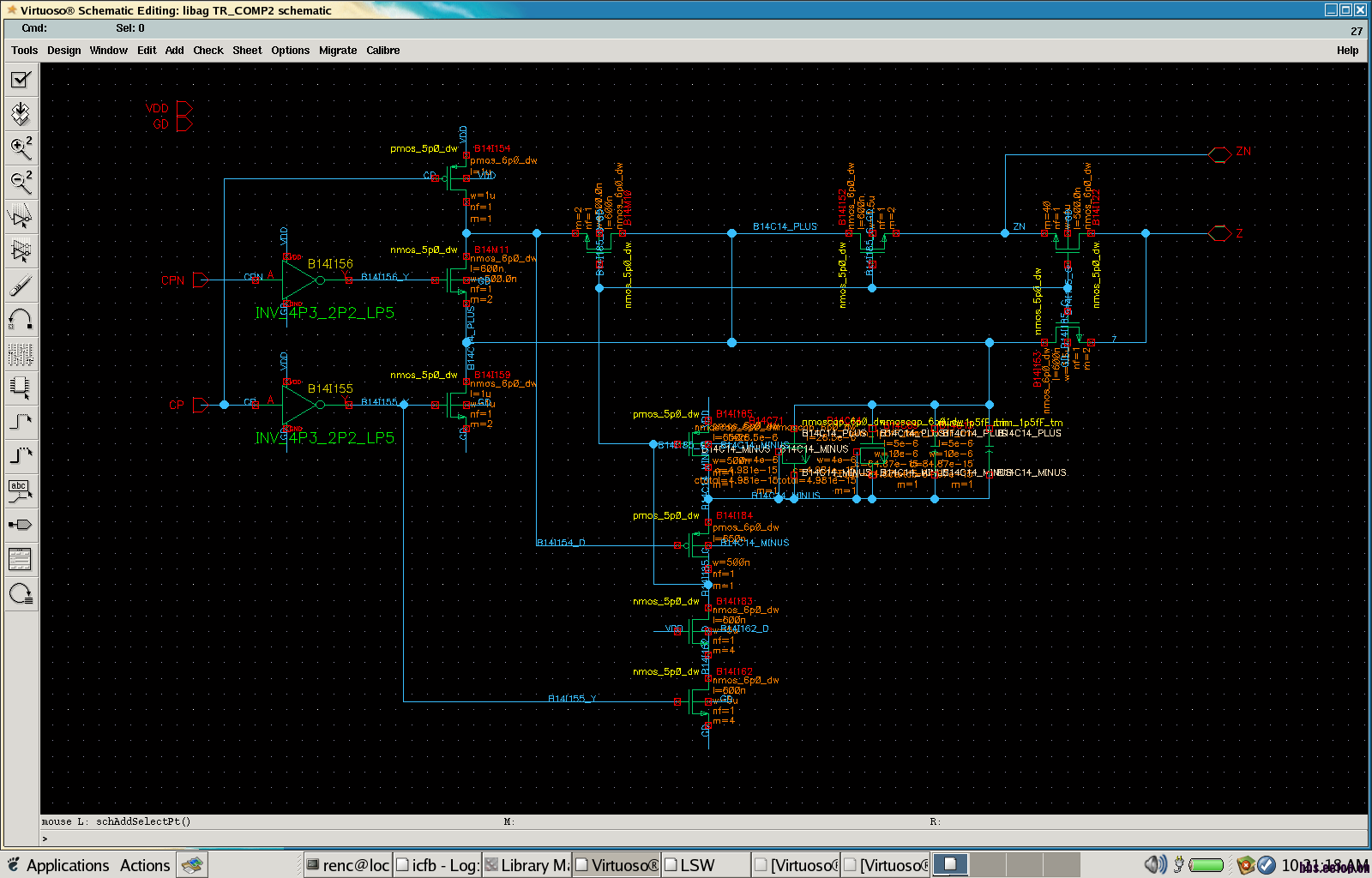

求电路分析。说出优缺点!

mark。

自己顶一下,是一个bootstrapped switch, 谁能详细解释一下。

中间密密麻麻,估计没几个人能看清楚是什么

图看不清楚的

不知道什么!看上去很厉害的样子……

把鼠标移到图标上,按CTRL+滚轮,图片就会放大,很清楚的。

我说个大概,不对的地方请小编指点

这个电路大致是说,在cp为low的时候,电路给电容充电,使电容两端电压约为vdd,

当cp为high的时候,将电容底电压端接到与输出电压相约的电平,正端给开关栅极供电,使nmos有足够的vgs

只是有些地方我没看懂,

1.按电路的结构,充电时,电容拉低的是nmos_cap的栅极,这样,nmos_cap电容很小的啊

2.cp变高的瞬间,B14I154_D端的放电通路可能包括B14I154的衬底,可能在衬底看到瞬间的电流,小心latch up的危险

中间躺着的nmos衬底怎么接看不清楚,这个也是latch up考虑的地方

其他我就看不出来了,请指教

我说个大概,不对的地方请小编指点

这个电路大致是说,在cp为low的时候,电路给电容充电,使电容两端电压约为vdd,

当cp为high的时候,将电容底电压端接到与输出电压相约的电平,正端给开关栅极供电,使nmos有足够的vgs

只是有些地方我没看懂,

1.按电路的结构,充电时,电容拉低的是nmos_cap的栅极,这样,nmos_cap电容很小的啊

2.cp变高的瞬间,B14I154_D端的放电通路可能包括B14I154的衬底,可能在衬底看到瞬间的电流,小心latch up的危险

中间躺着的nmos衬底怎么接看不清楚,这个也是latch up考虑的地方

其他我就看不出来了,请指教

基本功能就是一个节拍对电容充电,在另一个节拍的时候,开关MOS的栅电压等于= 预充电电压+输入电压。

理论上可以保持Vgs为恒值。(但是栅和衬底之间的电压会大于管子的工作电压。不知道这个怎么考虑?)

中间躺着的皆为NMOS管,衬底都接地。

预充电时,充电电流确实很小。另外,还希望jaylight 详细分析一下latch up的问题。

谢谢

小编这是面试召人么?

我看错了那只pmos,它没什么问题对于latch的分析,我比较保守,就是nmos任何时刻源漏都不要低于衬底,pmos源漏任何时候都不要高于衬底,看图很多时候只能看到DC值,开关切来切去的看tran多看几个点就这样,按latch up的理论来说,瞬间有小尖峰让衬底导通一下是不会有latch up的,但是衬底过电流始终不好。

躺着的nmos衬底都接地是没有latch up问题的,只要符合DRC规则的话,但是栅极电压就变成差不多两倍vdd了,这样是不行的,工艺说的3V,5V,是包括四端的,可能这个结构就要调整一下了,做这种开关,结构巧妙就巧在不过压,也不让衬底和源漏反过来

那只做电容的nmos_cap没有导通,电容还不如同等面积的mim呢,如果要省面积用它没有效果

电容旁边那个正方形的框框是什么东西啊?

mos cap

这个电路按分析电压时有过压的,但这个是流过片的,还望牛人过来分析一下!

booststrap switch 肯定会有搞过电源电压的节点,但这个“过压”没问题。关键是不要超过工艺限制的电压。流片验证没问题是说明这个过压没有超过工艺限制的电压。当然这个电路也就没问题了。你这个开关用在什么地方?开关频率是多少?多少的工艺?

0.18um process, 1.8 Volt voltage,

关键是栅极电压大于电源电压,但是NMOS的bulk连接的是地,这样的话,Vgb(略小于两倍电源电压)>工艺允许电压.这样分析是有问题的.

所以谁用过这种switch的话,请帮忙分析一下。

不明觉厉

这个电路是没有问题的,IEEE上有篇文章列出了一样的电路图,下次贴上来。

电路是没问题,工作分析也没问题,验证也没问题,就是你一直在问题。顶多这个东西的可靠性差点,器件的实际耐压都是大于fab给出的最大耐压值一定范围的,就像你设计电路的余量一样。所以验证也没问题,而可靠性差。

学习一下!

认识就是这样的,你怎么知道没有问题?

顶。

Bootstrapped Switch

Bootstrapped Switch

谢谢分享

芯片能工作的。gate电压pump到高于vdd时,source到bulk确实是高压,一般情况下确实承受不了。但此时NMOS处于开启状态,产生了沟道,起到屏蔽作用,gate到bulk电压分为两部分,1. gate到channel,即gate到source,2. channel再到bulk,即source到bulk,这两项都没有超过MOS耐压。这里的关键就是MOS开启形成沟道,起到屏蔽作用。因此不需要高压工艺。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请问比较器的失调误差offset会影响比较器的INL/DNL吗

下一篇:请教------“电路”,“电路分析”宝典