请教各位一个关于锁相环环路稳定性的问题

录入:edatop.com 阅读:

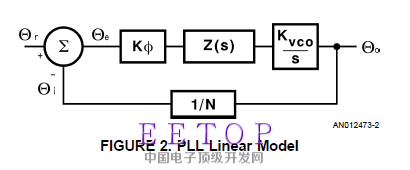

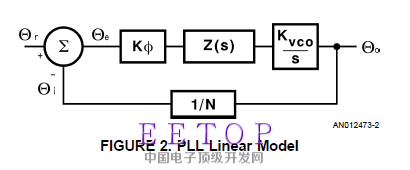

一个锁相环的线性模型框图如下:

Z(s)为环路滤波器,环路滤波器在锁相环中的地位很重要,小弟在设计这个环路滤波器时有一些不懂的地方如下:

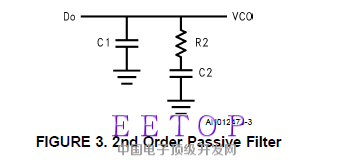

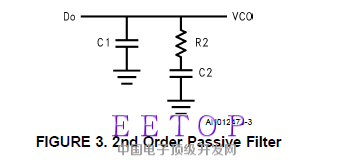

对于一个二阶无源环路滤波器:

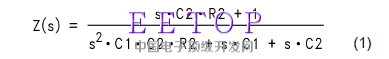

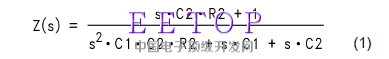

他的传递函数为

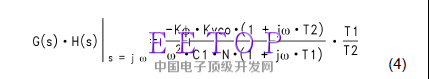

所以PLL的开环传递函数为

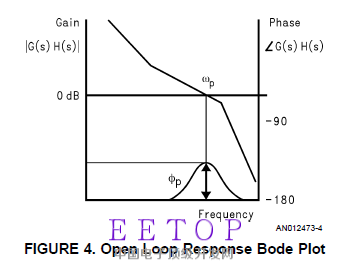

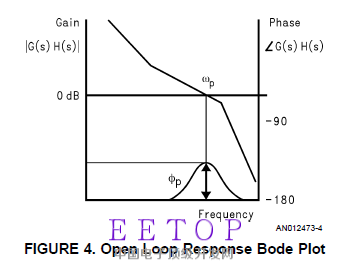

开环的频率特性如下图所示

我想问的是这无论怎么说,这个锁相环都应该是不稳定的啊,因为在低频段增益已经大于1,而相位裕度却为0。这不是标准的不稳定么,为什么很多文献也都采用这种滤波器作为锁相环的环路滤波器呢?麻烦大家了

Z(s)为环路滤波器,环路滤波器在锁相环中的地位很重要,小弟在设计这个环路滤波器时有一些不懂的地方如下:

对于一个二阶无源环路滤波器:

他的传递函数为

所以PLL的开环传递函数为

开环的频率特性如下图所示

我想问的是这无论怎么说,这个锁相环都应该是不稳定的啊,因为在低频段增益已经大于1,而相位裕度却为0。这不是标准的不稳定么,为什么很多文献也都采用这种滤波器作为锁相环的环路滤波器呢?麻烦大家了

小哥,你回去仔细读读书。反馈原理稳定性是说,当|H(jw)|=1,的时候,根据相位来判断稳定性。

但是从 原理上理解,就算相位裕度满足<60,如果在(低频处)开环增益大于1的情况下,如果负反馈的开环相移已经180度,那这不就形成了环路增益大于1的正反馈吗?

对于一个二类三阶PLL来说

频率趋近于0,相位趋近180度,但是只要频率>0,相位永远不会达到180度,只是趋近。虽然phase margin很低,但是不会振荡。环路会有DC吗? DC意味着鉴相的相位差完全不随时间变化,会出现这种情况吗?实际上应该不会出现这种情况。所以不用担心稳定性。

但是对于二类4阶以上的PLL,相位会出现穿越180度的情况,高频区会有稳定性的问题;

请参考这个帖子的讨论

http://bbs.eetop.cn/viewthread.p ... p;page=1#pid3056233

多谢!我去看看,谢谢你

谢谢分享

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:ADS仿真CMOS反相器问题

下一篇:求助关于CDR系统建模