求助!cadence中生成gds文件时warning相关

录入:edatop.com 阅读:

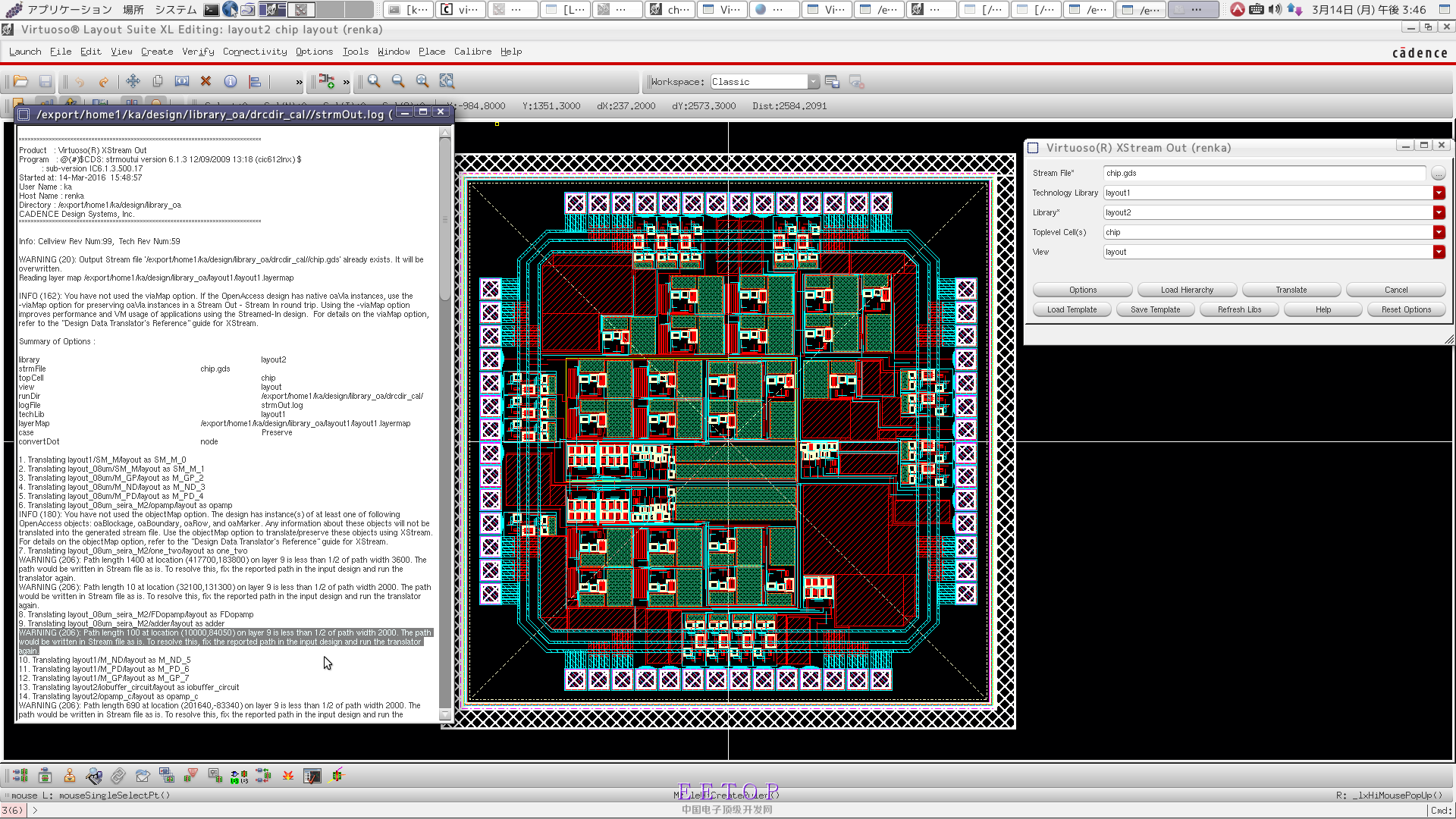

Cadence(6.13)芯片设计完成后export时候,提示0错误17个warning,17个大概都是下面这样的:

WARNING (206): Path length 1400 at location (417700,183800) on layer 9

is less than 1/2 of path width 3600. The path would be written in Stream

file as is. To resolve this, fix the reported path in the input design

and run the translator again.

设计时也用不到5层以上,为什么会提示9层的警告?而且

(417700,183800) 这个坐标太大了,芯片最大x坐标也就是2400左右,完全搞不懂,有谁遇到过类似问题?

- -自己顶下

lihai

有遇到过么..话说lvs验证时都是0warning么?

layer 9 要看 tech file 吧, 查查位置 (417.7, 183.8) 的 layout

好的谢谢,坐标 有点不懂,为什么是

(417.7, 183.8) ,之前一直不太注意warning,觉得没错就ok的。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。