运放的设计

录入:edatop.com 阅读:

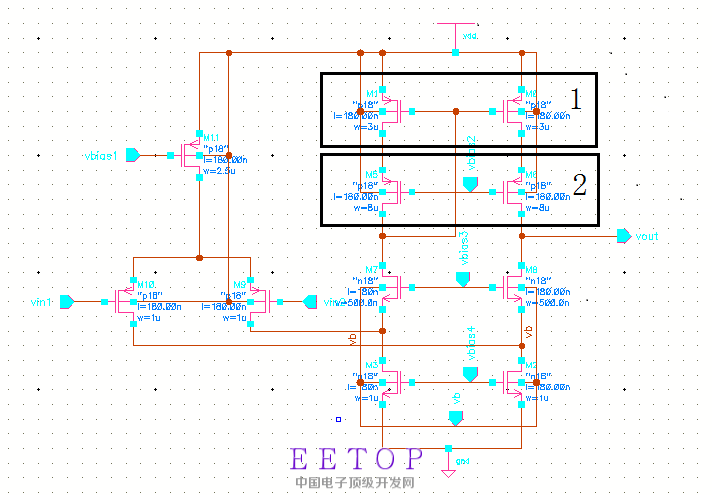

设计如图所示的普通折叠式运放,但是在设置工作点时,遇到了点困难,调节了半天也没能解决,特在此求助各位。

刚开始设计玩的时候,方框1中的两个管子处于线性区,其他管子都在饱和区,然后我就尝试调节了方框1和2中几个

PMOS管的尺寸,但是当我把方框1中的管子调饱和了,方框2中的管子cadence显示region为3,调了半天也无法保

证所有管子共同处于饱和区。

请问设计中存在什么问题呢?应该从什么角度入手去解决呢?

谢谢各位了

我也正在学做运放,但是cadence死机了我强制关机之后,不能打开编辑环境了。有什么解决办法吗?做到一半...

应该是锁定了,你进到你设计电路对应的目录下,把文件后缀最后三个是lck的文件删掉就可以了

我把带lck后缀的文件都删掉之后,再输入icfb&是不会再出现 ...is already locked by some process, 但是像

不会吧,输入icfb以后直接弹不出来编辑界面呀?

嗯嗯 就是只有

这个问题,我没有遇见过呀,我每次被锁定了就把我给说的那个文件删了就都好使。

你看我发的图,底下的窗口只有两个,没有可以编辑的面板出现啊

1进入线性区,说明1的W/L偏大,只能使其进入线性区来匹配偏置电流;2进入亚阈值区,说明2的Vgs偏小,使得Vgs约等于Vth。

解决办法我觉得可以减小1的W/L的同时减小2的栅极偏置电压;或者仅减小支路的偏置电流试试。

这中运放还是比较难调的,但是如果你设计好BIAS,还是有办法的,一般情况下,方框一你一定要饱和,而且留有足量的margin,对于cascode管子,你可以适当的放一些margin。

恩恩,谢谢,我后面调整了一下偏置电压,就饱和了。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。