ESD 失效如何解決?

Process: UMC0.13um 1.2V/3.3V

Chip: Multi-power domain,有數位、類比 1.2V & 3.3V, 使用Faraday提供之I/O並且照其規則layout,內部電路為自行設計。

狀況:HBM 2kV-- All pass。

MM 200V-- 5個不同power domain的1.2V VDD-VSS (+)(-)fail,其它都pass。

CDM 500V-- MM fail的pin,也同時fail。

目前分析顯示損傷應位於內部電路,ESD保護電路無傷害。是否表示於esd 測試時,保護電路未成功觸發,請問此狀況要如何解決?

感謝大家的指導!

例如VDD1 VSS1 VDD2 VSS2。VDD1与VSS1之间的正负MM mode不过?

其它IO对VDD1和VSS1打ESD也可能经过这个VDD1-VSS1路径的吧,都过了吗?

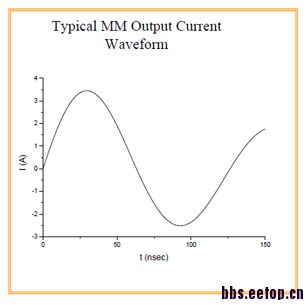

看了HBM MM CDM的比较,后两者的上升斜率和到达的电流更高。觉得有可能是电压上升太快,在ESD器件开始流过大电流并钳位之前,其它地方击穿了。

小编确定VDD1对VSS1打负电压也会失效吗?

从你的叙述看,应该是fail在不同power domain的interface.

建议check一下power clamp与interface之间距离是否太远(VDD/VSS line电阻过大),可以就近加一些power clamp cell.

这个问题如果能看到整个电路的schematic/layout会比较好分析,可否提供?

感謝您的回覆,我說明得不夠清楚。

目前的打法是 vss1 vss2 .... vssN 都連接在一起打。所以是 VDD1-VSS 之正、負MM ESD fail。

其它IO對VDD、VSS 都有pass。

*目前如你所說,可能是esd作用之前,就擊穿內部電路,不知應如何解決。

*正負的確是同時都fail。正負各做3顆sample,至少都fail兩個,正與負pass or fail結果十分一致。

您好。在做VDD-VSS(+)(-)測試時,VSS是bond在一起打esd。

是否表示同一個power domain的VDD-VSS就已經無法pass? 而非不同power domain之間的問題?

謝謝!

貌似MM模式的电流波形是正负的,所以测试的时候正和负失效差不多。从其它的IO往VDD和VSS打ESD或者也经过VDD-VSS路径,但可能延缓了这个电压的上升(等效为一个串联阻抗)。

工厂提供的ESD有分IO ESD和power clamp吧,VDD和VSS之间用的是GCNMOS?

Hi,

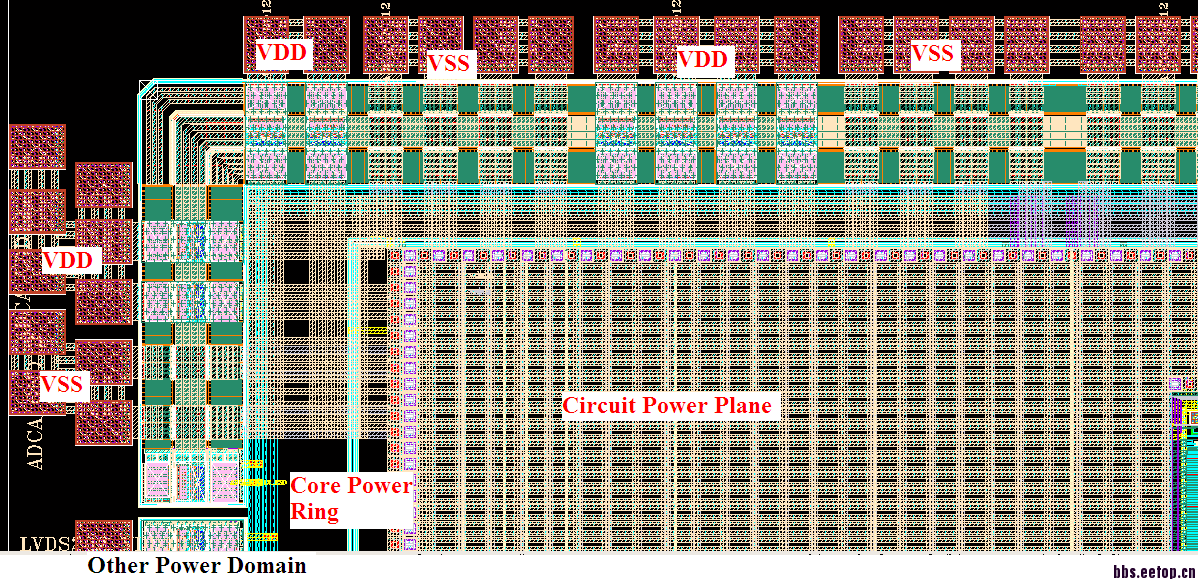

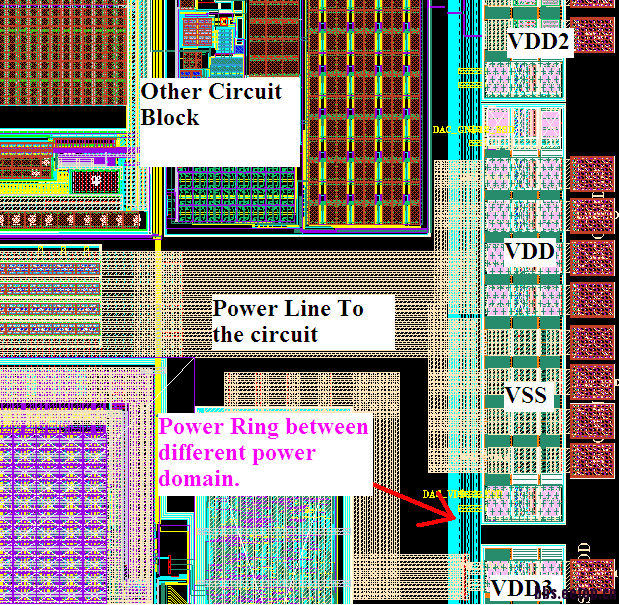

我傳了其中兩個power domain的截圖,在打esd時,為圖中vdd 對 所有vss(bond together)去打。請多指導! 謝謝。

是gcnmos沒錯。

但是在這種情況,是ic layout有問題嗎,或是需要重新設計esd保護電路?

typical來說應該是在IO作好esd防護就好嗎?又或者是在內部的每個block需要額外再做單獨的esd保護電路呢?

謝謝

Process: UMC0.13um 1.2V/3.3V

Chip: Multi-power domain,有數位、類比 1.2V & 3.3V, 使用Faraday提供之I/O並且照其規則layout,內部電路為自行設計。

狀況:HBM 2kV-- All pass。

MM 200V-- 5個不同power domain的1.2V VDD-VSS (+)(-)fail,其它都pass。

CDM 500V-- MM fail的pin,也同時fail。

目前分析顯示損傷應位於內部電路,ESD保護電路無傷害。是否表示於esd 測試時,保護電路未成功觸發,請問此狀況要如何解決?

分析-HBM 一般遵守FAB的ESD guildline可以pass 2KV

MM与CDM的ESD电路设计不同于HBM的ESD电路设计,需要再设计

也就是说,如果芯片需要PASS HBM/MM/CDM,需要有3套ESD电路

从你的芯片版图IO环上可以看出,是电源环是物理隔离的,没有形成回路,打ESD导致往高压内部电源地网络中去啦,所以内部器件损坏。

感謝提示!

請問一下 所謂的3套esd電路具體來說是怎樣實現! 是否可以說細一點?

for mm & cdm 分別要用怎樣的架構呢?

謝謝 Orz..

請問一下,所謂沒有形成回路是什麼意思,可否說明一下?

目前的layout方式是照fab建議的方式,跨domain的lay法也是,感覺上應該沒有什麼大問題才對,麻煩提示一下,謝謝!

问题解决了么 ?

layout应该画得也不好

真有意思,最该pass的VDD-VSS出问题了。

这么多power domain很危险的啊,domain之间都必须加比较宽的guard ring隔离。

另外可以参考一下标准IO VDD和VDDH之间是怎么防备ESD的,除了VDD-VSS和VDDH-VSSH的clamp,

VDD-VSSH和VDDH-VSS之间也是有clamp的,另外VSS-VSSH之间有back-back diode,还有保证

有一个比较粗的通路当做ESD buss (在标准IO里面是VSSH).

你这么多VDD的domain,有保证不同的VDD对不同的VSS有clamp吗?不同的VSS之间是back to back diode相连吗?如果没有前者,那你的ESD buss只能有VSS来承担,那可得画得比较粗一点。还有两个power IO之间不能超过200u噢

做一下失效分析,拍照片

感謝感謝!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。