PLL中VCO相位噪声的仿真能否带分频器负载?

录入:edatop.com 阅读:

小弟用0.13μm工艺设计一个16GHz的PLL,目前还在设计VCO和分频器的阶段。小弟发现VCO空载或者只带一个CML buffer负载时,在1MHz频率offset处的相位噪声大概-100dBc/Hz左右。但是当小弟把一个CML latch构成的除二分频器加到VCO buffer后面时候,再仿真VCO输出的相位噪声,发现已经严重恶化了,在1MHz频率offset处甚至连-90dBc/Hz都达不到,并且相位噪声的曲线也不是一条向右下角的直线,而是在频率offset增大的时候变得平滑。小弟不知这是本来就有的现象,还是没设计好。想问下大家,我们一般说VCO的相位噪声仿真的指标,都是在空载的时候说的吗?谢谢诸位。

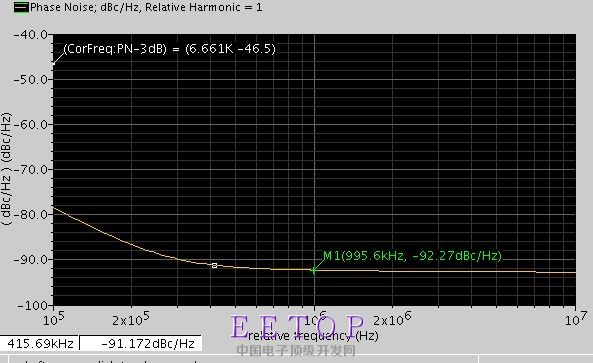

这张图是级联了一个分频器后,VCO输出的相位噪声曲线。分频器带了一个buffer,后面是空载的。VCO在20GHz左右,分频器分到10GHz.

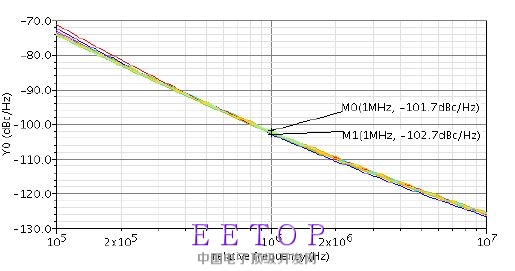

VCO空载时候仿真的相位噪声大概是这样的:

目前的电路只有一个VCO和一个分频器(第一级),是开环的。

是分频器的一些失真耦合到VCO上去, 好深奥

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。