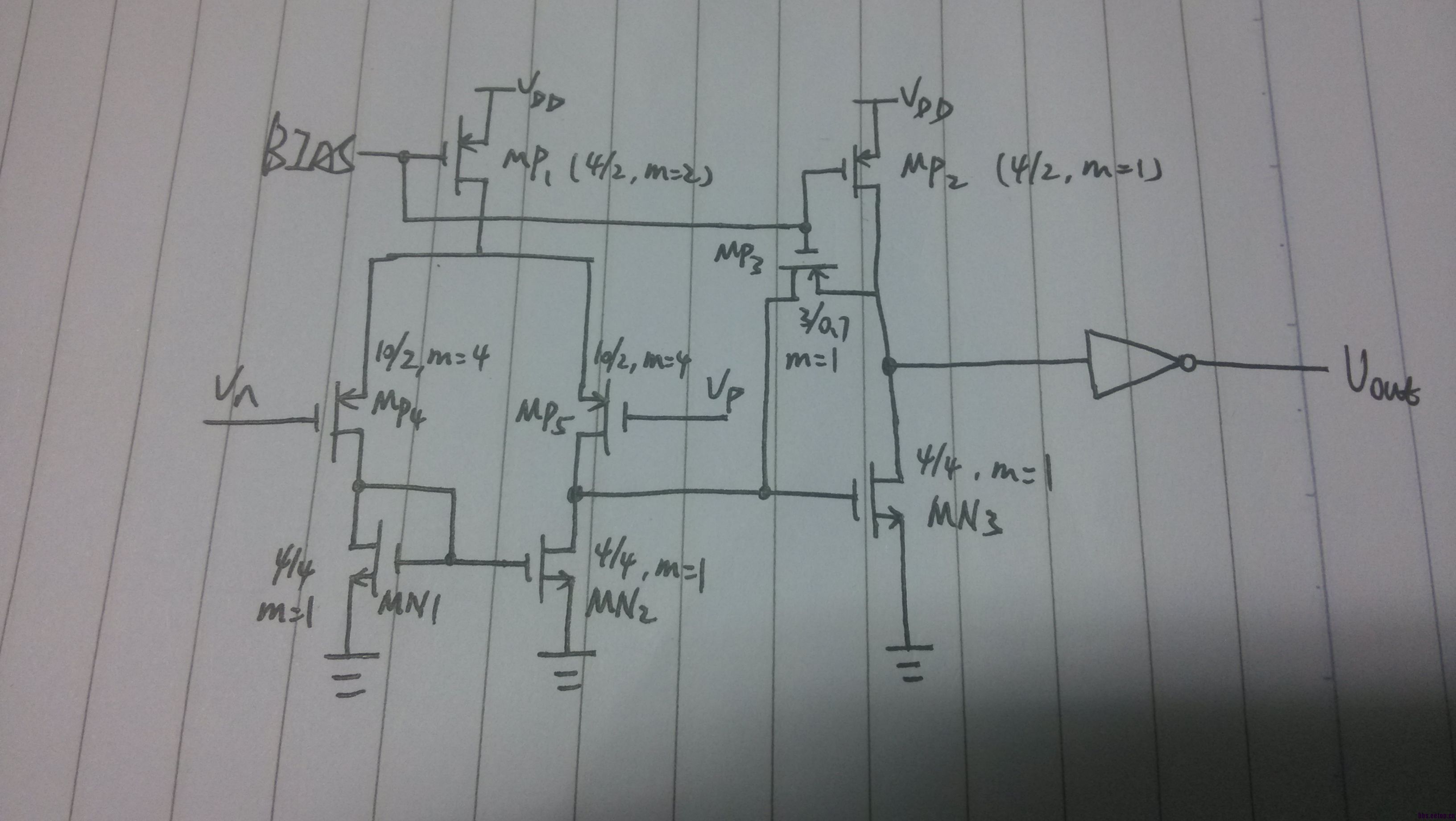

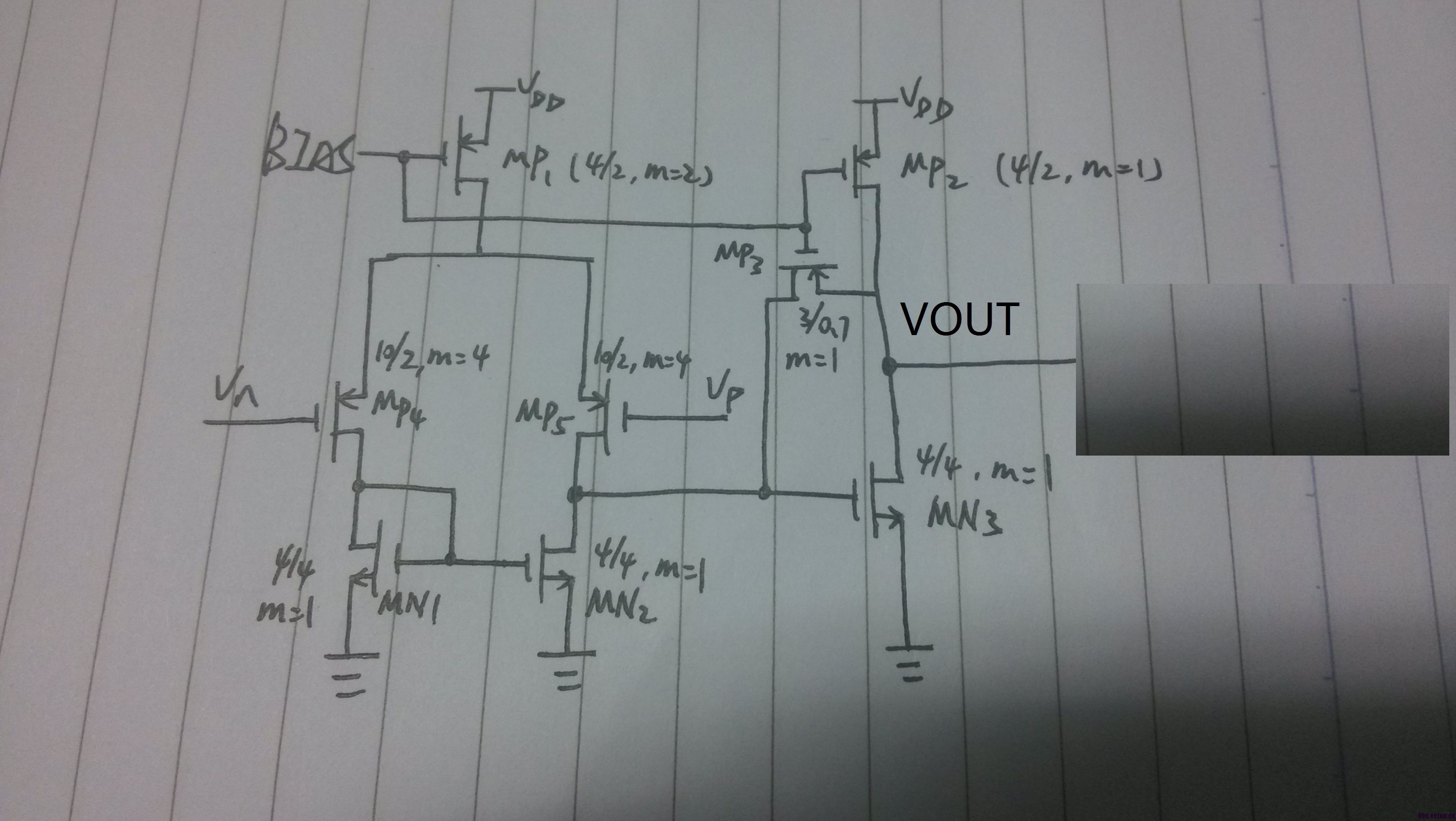

请教下面的这个比较器中的第一级和第二级跨接的PMOS管作用是什么?

求解毒!谢谢

前几天不是刚有人问过嘛,自己找找吧!

提供一个前馈通路,提高比较器的速度

好吧 我找找看

关于这个前馈通路能不能再多说几句?PS:看阁下的昵称,请问你是江师兄吗?

不能沉啊,哪位大侠过来给点拨一下!

顶下,学习了。

弄懂没有啊,小编?给我讲讲,想不通啊

不让比较器打死了,老婆赶人了,改天说

我基本算是搞懂了,MP3的存在使MN3/MP2 drain 有一个到MN3 gate的负反馈,就是让MN3/MP2 drain 达到高电平时,使MP3导通,从而使MN3 gate 的电压升高,MN3稍微导通使MN3/MP2 drain 电压略微下降达到4.7V,从而MP2不会完全cut off,这样在往下个状态翻转时MP2的速度会更快,这样比较器的速度就提高了。不知道分析的对不对,请各位指点。

收藏,以后可能用到~

seeing

提高比较器的速度吧

怎么提高?

学习了

那是一个正反馈的作用

哪个正反馈环路?

恩,是的,你是?

这个就是一个前馈通路,提高速度,当输出节点电压升高,运放第二级输入管的电压升高,形成一个正反馈,提高运放的速度

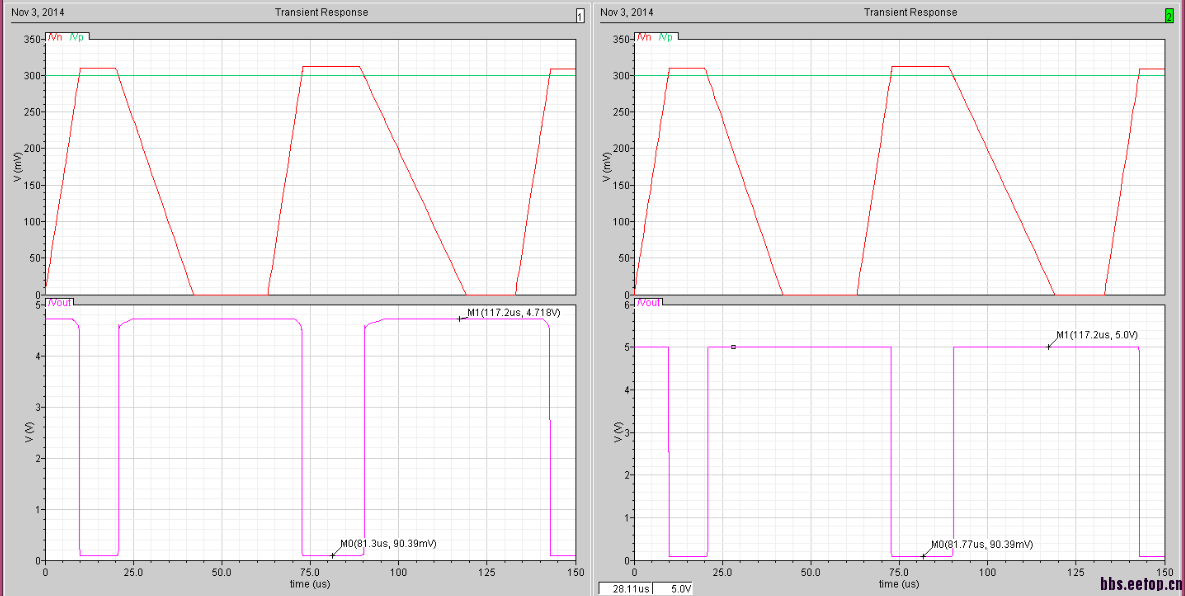

仿真结果没看出来比较速度快了?

结果上没看出来速度有变快啊

頂上學習!

恩 对 我之前认识有误,仿真也很粗糙,具体的影响还要仔细仿真一下,不过还正在学习中·····

是这个意思吗:在MP2/MN3 drain 由高电平往低电平转换的过程中,由于MP3的存在使得MN3 gate 更快的达到高电平从而使MN3更快的导通,加快了MP2/MN3 drain 向低电平转换的速度?

学习了

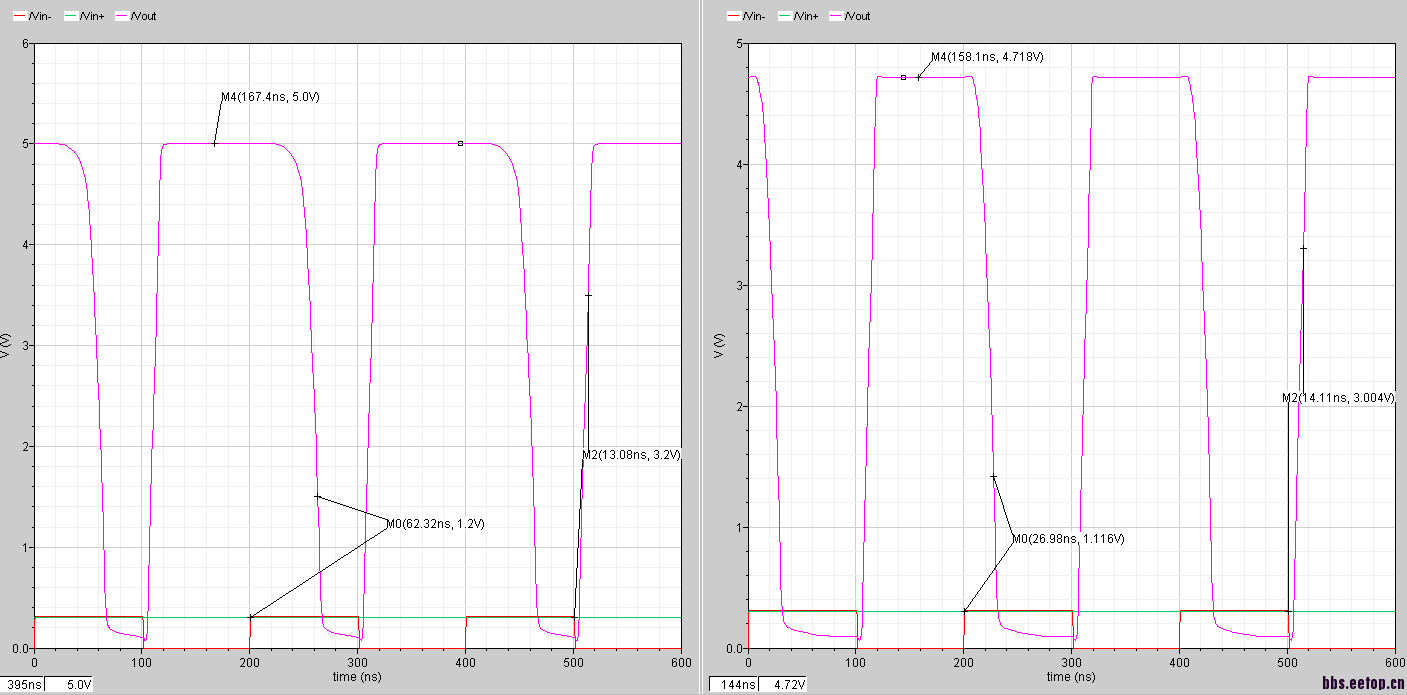

左边是没有MP3的结果,右边是有MP3的结果。

正输入端电压固定:Vin+=300mv。 反向输入端信号是周期为200ns,占空比为50%,高电平为310mv的时钟信号,用来模拟Vin-端的激励。

Vout是MN3/MP2 drain(不是缓冲器的输出)。

仿真工具spectre,CSMC 0.25μm BCD 工艺。

按照Allen的说法,认为comparator的Vout分别达到Voh的70%和30%时完成向高电平和低电平的转换。

仿真结果可见:MP3在Vout由高电平向低电平转换时明显的缩短了延迟时间,跳变延迟由62.32ns缩短到了26.98ns,Vout由低电平向高电平跳转时基本不会起作用,这和前面帖子的分析是一致的。

还是觉得奇怪!

marking 不太实用!

请问小编,这种电路在Allen书上哪一页?谢谢!

跨接的pmos管等同于半个施密特触发器,直白讲就是不允许输出电容在小电流的情况下放电。

363页,图8.2-1,这种两级比较器也许是最经典的结构了,但是Allen没讲到过两级跨接晶体管改善速度的结构。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。