sigma-deltaADC采样时钟不连续对ADC的影响

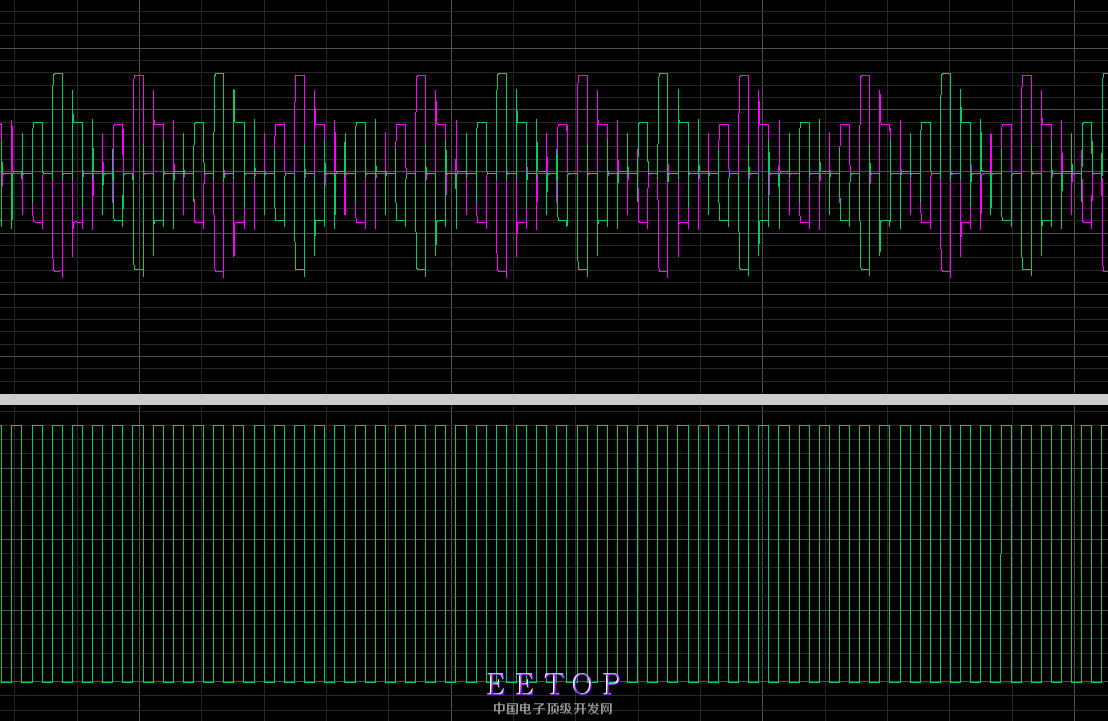

对ADC的会产生什么问题?时钟信号如图所示:

在实际设计的二阶单bit sigma-deltaADC中,一个信号通道输入时采样时钟是连续的占空比为1/2的时钟,另一个通道是如上图所示不连续的

采样时钟。第一个出来的结果正常(接共模时输出为0),第二个接共模时输出有一个较大的值,不知道是否是这个时钟差异造成?因为除了

时钟外其他条件都一样了。

请各位大神不吝赐教~[:\rose]

顶一下,希望大神能够尽快帮我解决这个问题

如果是开关电容结构的ADC, 从原理上看, 如果时钟停顿时开关也不动, 那系统的状态将维持不变, 而输入信号又是直流没有变化, 那么当时钟从新继续时, 系统应该会和正常时钟驱动下输出一样. 建议可以对比一下两个ADC在时钟停顿前内部节点的电压是否都一致, 然后看看停顿后的ADC内部节点的电压是否都保持住了.

谢谢指点。波形都是一样的。下图是第二级积分器的输出@输入接共模。

能否求大神用matlab建个模型仿真一下这两种clk对sigma-delta的性能是否有影响。

谢谢。

从波形看如果把时钟停顿的那一段去掉, 两个ADC的波形是一样的, 说明状态是保持住了并且继续下去的, 这样输出结果我觉得应该是一样才是.

"第一个出来的结果正常(接共模时输出为0),第二个接共模时输出有一个较大的值," ADC输出是0和1的序列 , 请问你是如何对结果做处理来比较大小的?

谢谢答复:

比较器的结果都是通过时钟沿来抓的,然后串行转并,然后在对数据进行滤波,所以两种情况结果是一样的,

实际测试时的测试结果的差异其实两种情况下ADC本身的offset差异(实际计算两种情况下的offset差了6~7倍)。

所以这两种时钟确实是一样。我还要找找我电路里为什么两种情况下offset会差这么多。

ct 结构?

开关电容结构

抱歉了,最后发现是数字部分的数据处理有问题。实际ADC等效offset为1.8mV左右(@ref=600mV),有点大,初步判断可能是里面的offset校正电路产生的。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。