DC-DC中的带隙振荡:时钟开启时带隙振荡是什么原因?

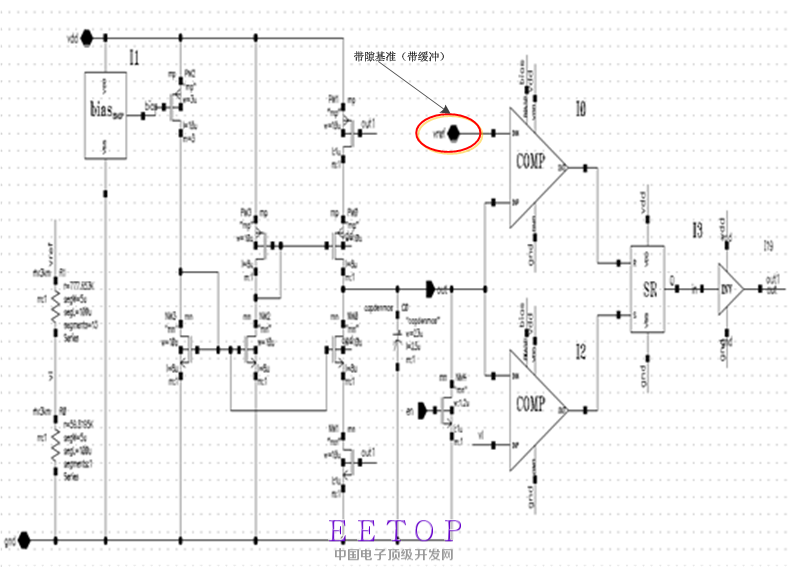

带隙基准1.2V/约1.8V,电路中基准已全部用缓冲器接出,

带隙基准1.2V/约1.8V,电路中基准已全部用缓冲器接出,且测试时也排除到了示波器阻抗的影响。

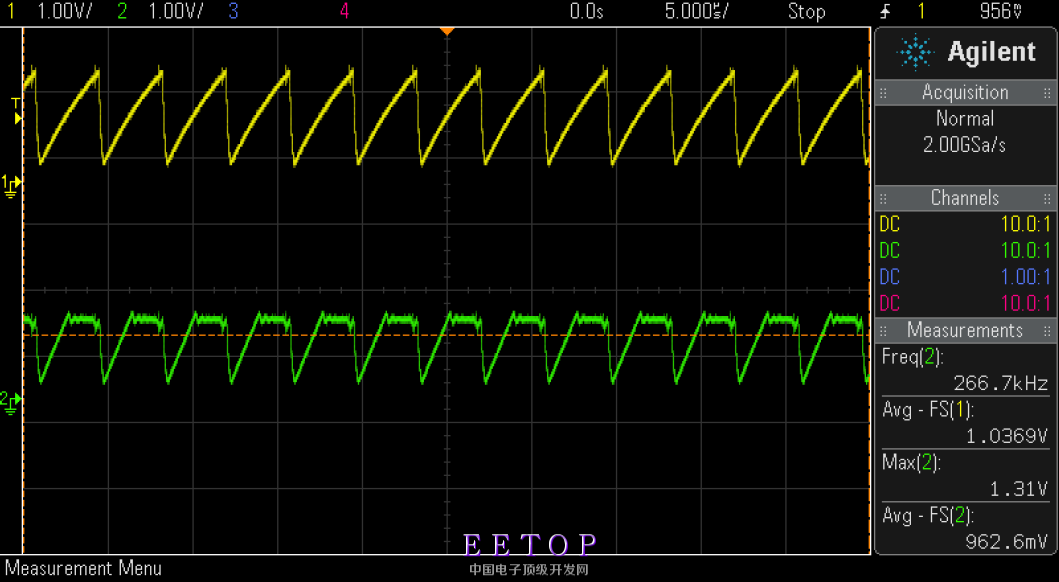

时钟使能开始时,振荡;时钟使能关闭时,带隙电压正常。

振荡的原因是什么?版图的设计能有多大的影响?(没有做隔离)

基准与clk线并着走的吧,而且基准对地没加多少电容。

kickback 产生的影响很小

谢谢回复!基准输出和SLOPE输出确实有一段是并着走的:160um的长度,1.5um的间隔,400kHz的频率,请问这样的版图布局是振荡的确切原因吗?最好能给个依据(理论 OR 实际经验)~ 另外,基准对地确实没加电容,测试发现基准缓冲输出后,加上100uF的电容,振荡虽减弱但仍存在,且均值在正常值之下~

高手们有没有这方面的经验~

既然版图没做隔离,加上有并行的线有这样的影响基本可以确认是版图问题了。

但不尽然,时钟的pin和带隙的pin距离有多远?端口或引线太近的话也有影响。可以对比一下单独测试带隙的pin和两个pin一起测所得的波形。

谢谢回复!带隙和SLOPE部分的pad在版图上是上下分布的,应该够远。之前有单独测试和共同测试过,现象是:SLOPE工作的时候,上电时候基准输出是正常的,但马上会振荡;有时候触碰一下芯片及其周围,基准输出会一段时间变正常;总之,输出很容易振荡。

请问,能不能有说服力的理由说明是版图的哪些问题,谢了~

OSC的两个比较器,上面的带buffer了,下面的也带了?

带隙基准经过电压缓冲接入后,用电阻分压产生两个电压作为比较器的基准电平(V_high、V_low)。但是比较器的输出没有加buffer而直接接到RS触发器也许是个问题~

如果是版图内部的原因,用手碰碰周围什么的,应该不会出现带隙恢复正常这种情况。

你的探头连接是怎么连的?示波器的探头的地要尽可能的接近被测端,才能保证尽量不pick外部的电磁波。

”触碰“的意思是:带隙输出在振荡的过程中,触碰下有时候带隙输出正常(怀疑是给芯片的某些PAD给高电平了,一些PAD引出后在PCB板上有通孔),但很快又会振荡了。 另外,400KHz的频率应该不会有电磁波干扰吧~

带隙基准有没有在芯片上加buffer之后再接到示波器?如果带隙基准没有足够的输出电流能力且不再芯片上加buffer,那么有可能测到有问题。

有的~

如果一定要碰到pin脚才有效,有可能置高了某些pin,也有可能是改变了周围的电容,减少了天线效应(这个天线效应不是IC中的那个天线效应)。调幅广播起点也就550khz,你的400khz又不是正弦,二次谐波有辐射很正常。我经常测试某些高频大信号的时候,手放到附近就会引起信号变化。

嗯,想请教下:版图的问题会是振荡发生的主要原因吗?测试中观察到带隙振荡的波形和并行时钟线的波形特征还是相像的(方波、三角波)

这个我很难确定。一般说来这么相像有两种可能,一是探头pick到了信号;

二是你给bandgap供电的电源同时给buffer供电,buffer驱动量太大而电源动态响应不足导致欠冲。但后面这种情况仿真也可以看出来。如果担心是这种情况可以测测在时钟工作时bandgap供电端的电压。

话说你给bandgap供电是否设计了独立的ldo?

感觉PSRR不至于这么差

带隙是电源直接供电的,电源的驱动能力是足够的,应该不是电源的问题。

不是psrr的问题,如果psrr的问题的话会有过冲,这里只有欠冲。

我说的电源问题是说电源被拉到带隙正常工作点以下。当然我是猜测。

不见得,你先测测。一般的稳压电源动态响应并不是很高。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。