SAR ADC仿真~~

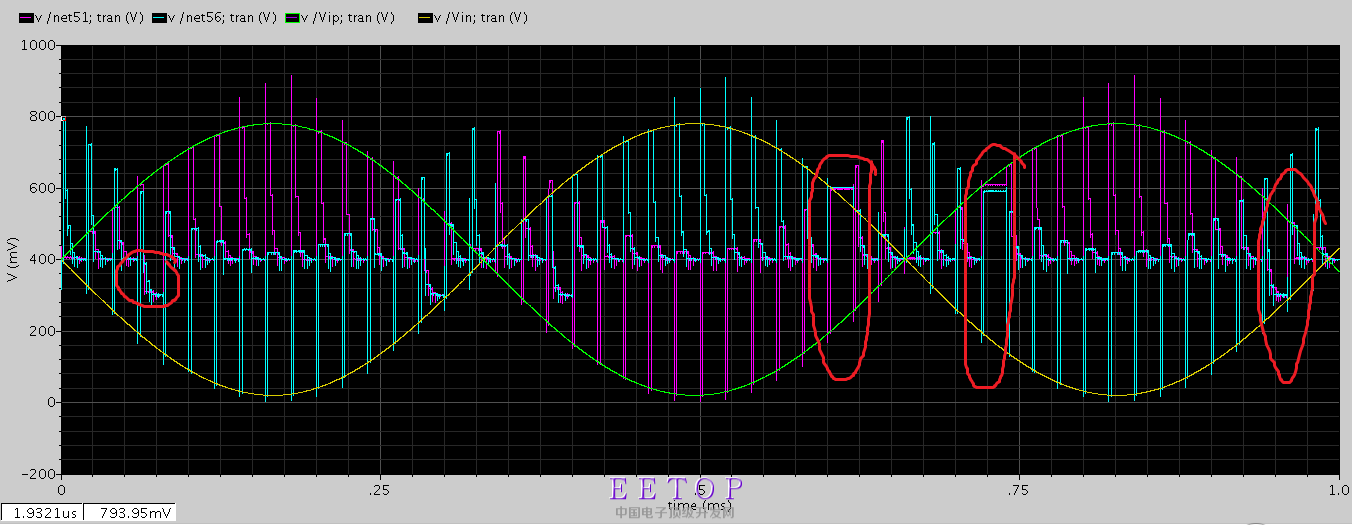

这是SAR ADC的比较器输入端的波形,可是有的周期两个信号逐次逼近不能到共模电平,而有的周期直接就没有逐次逼近,请问大神们,有人知道是什么原因吗?我该从哪里修改电路呢?

自己先顶一个!

是否是比较器高位判断错误,导致后面系统进行修正,但是无法修正到正确值?

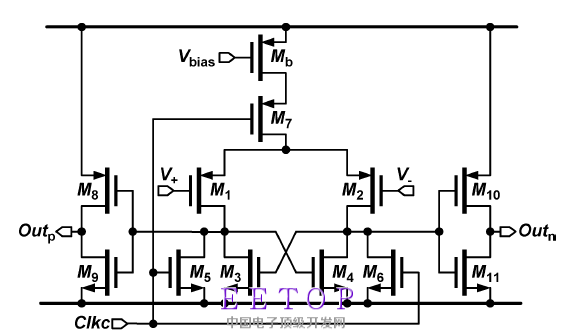

比较器用的什么结构

如果是比较器判断错误的话,那前几个周期也可以进行逼近啊,到了第四个周期就有问题了。

动态比较器

我觉得你完全可以一个个用理想器件慢慢排除问题啊

明显的逻辑出问题了。

请问一下,cadence里面有双端输入和输出的理想比较器吗?我只找到单端输出的哎

如果逻辑出问题了,之前的周期也能逐次逼近哎

可以用这个单端的再加一些组合逻辑门组成你需要的动态比较器啊,还有,一看你这图就知道你参考的是10年的单调切换技术,哈哈

也可以自己用veriloga来写你需要的比较器。不过我没试过,写代码一直是我的阿克琉斯之踝

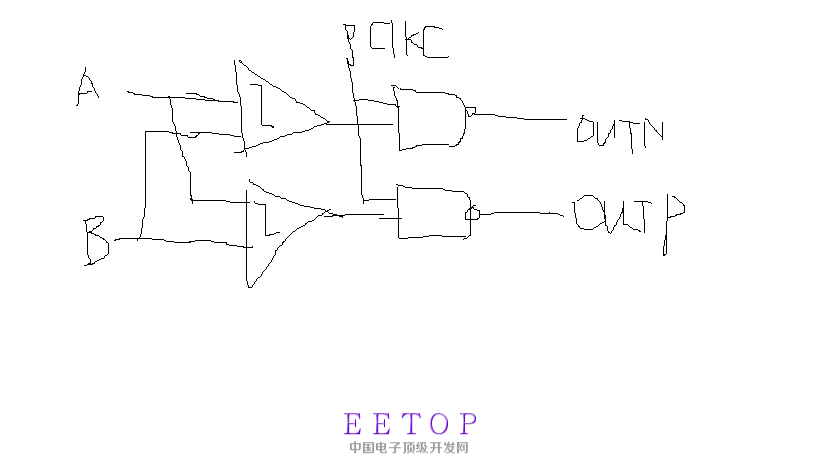

大神,能不能说一下怎么用逻辑门搭双端比较器,网上没有什么资源啊

后面用与非门还是或非门看你的逻辑要求,前面的比较器就用你说的理想双端输入单端输出的,设置下参数

哦,好像比较器输入端的连接有点小问题,你试着看看,就是这么回事

谢谢啦,我试试去

现在问题解决了吗

还木有

下次看波形的时候,看比较器双端输入的差值哈

请问你知道小输入信号下比较器的速度该怎么仿真吗?

这些错误的周期就是比较器两端差值很小的时候~

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Cadence IC5141上如何对不同器件的Corner进行自由组合仿真

下一篇:请问关于用ocean仿真corner的一个问题