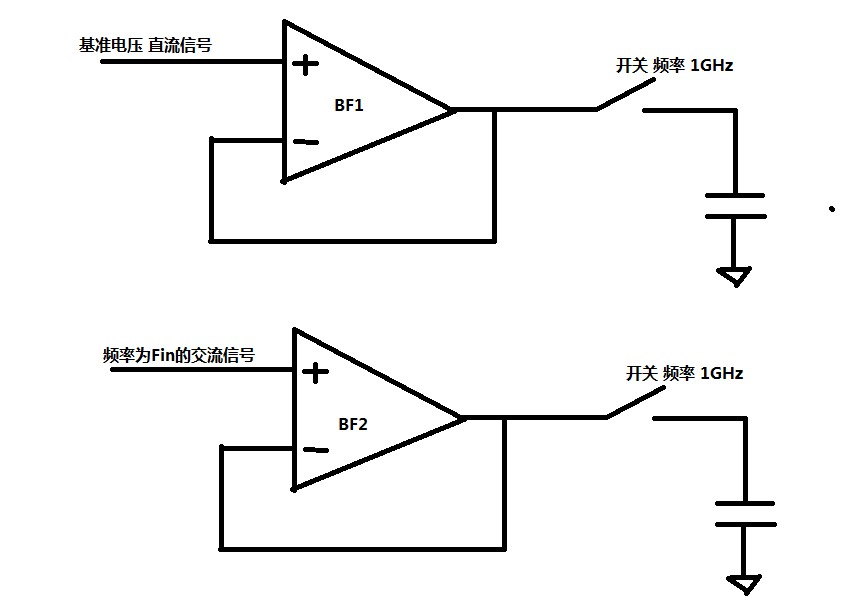

请教两个buffer的带宽应该怎么设计

BF1放大的是直流信号,所以带宽不需要很宽,

BF2的带宽要大于信号频率

是这样考虑吗?

BF的带宽要不要考虑开关信号的影响?请各位前辈指点

open loop BW(unit gain frequency)=1/close loop time constant

第一個buffer 看你要settling 到幾bit 一般 一個close loop time constant = 1.5bit (log2(exp)~1.5), 考慮analog device的variation 一般我都用1 time constant = 1bit 來簡單算一下

buffer的整個充電時間 (buffer 1 & buffer 2

)= skew rate time + linear settling time (這部分就是看settling 到幾個bit)

第二個buffer除了要對C充電 所以除了充電時間外 還要扮演filter的角色 那會有信號 lag 看你希望有多少誤差 1G的clock要高解析會非常耗電

谢谢指教 诚如你所说,1GHz的开关信号buffer确实很耗电。

建議直接用大顆 transmission gate (小電阻)就好了 如果前級推力夠 buffer 1 & 2 就不要了

请问关于您所说的“open loop BW(unit gain frequency)=1/close loop time constant

第一個buffer 看你要settling 到幾bit 一般 一個close loop time constant = 1.5bit (log2(exp)~1.5)”有相关的推导资料么?最近在做一个Buffer,不知道Buffer的参数如何确定,谢谢!

我看到小编有做过SAR的设计,能不能给小弟一些关于SAR buffer的一些资料么?最好有一些指标的推导,万分感谢~

你好,我也没什么心得,谈谈我的浅见。在公司里看到的buffer其实很简单,就是一个单端输出的两级密勒补偿运放。ADC_Vref_Buf根据你的采样频率来确定带宽(建立时间和建立精度)。比如SAR ADC每次比较的周期是T=1us,ADC的精度是10bit,那么最好你的buffer能够在0.5*T建立到>10bit的精度(7.2*tao)。tao是运放的时间常数,tao=1/(2*Pi*f-3dB),然后求出f-3dB ==》 GBW,一般都要求相位裕度在90度左右,不要有振铃。 然后再考虑buffer的offset和噪声,也就是管子的(W*L)。在满足以上spec下功耗越小越好。

恩恩,好的,受益匪浅,谢谢啦~

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。