PGA电路线性度问题

录入:edatop.com 阅读:

PGA电路在增益达到30dB时,带外IIP3为-10dBm,这个值算低吗?有什么方法可以提高吗?

没人么。

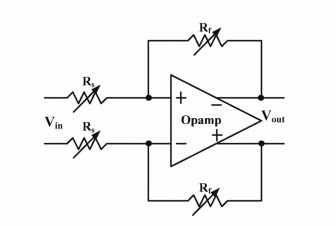

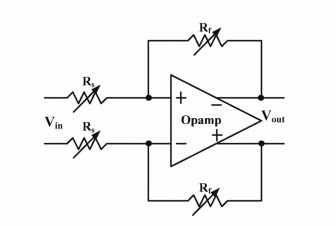

PGA 可變電阻是使用 MOS linear region ?

還是使用 一堆 switch 切換電阻?

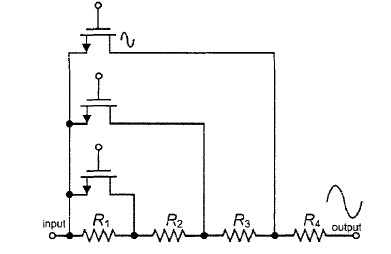

是用MOS开关切换的

How to define 带外?

如果真是带外,通常说来,你这还差了点,一般带外blocker都比较强

但是如果是带外,PGA貌似也最好并个C在feedback R上,对带外有一定的滤波效果

另外仿真出来的IP3还需要处理一下,才是真正的带外IP3

我是这样定义带外信号的,即PGA电路-3dB带宽外的频率。

用PSS(从-30dBm输入功率开始扫描)仿真出来的IIP3点要怎么处理才是真正的带外IIP3?

想请教下小编,您的开关衬底如何处理的?接vdd/2还是接地?如果接vdd/2的时候,断开时衬底和源之间的pn结可能导通(信号摆幅比较大的时候),会导致衬底信号串扰进来;直接接地的话由于衬偏效应的存在开关导通电阻随工艺变化很大,进而影响pga增益步进。最近做这个项目碰到这问题,想请教一下,谢谢~

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:layout netlist对mos的描述是否也是D G S B顺序?

下一篇:nanosim + vcs 仿真问题