电路的耐压问题

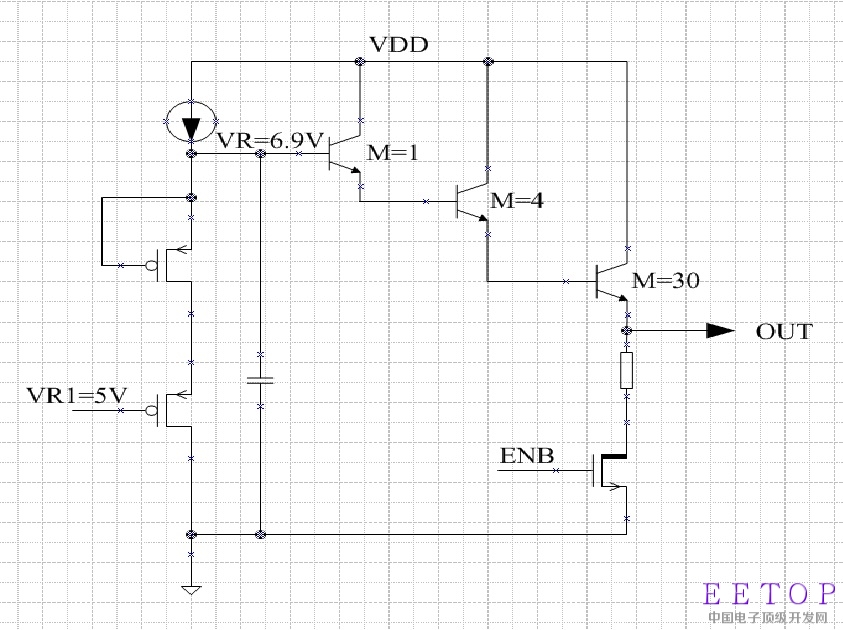

如图,VDD为芯片电源,OUT为输出电压。当电源电压在12V~20V的时候,OUT的输出和设计值一样,大约是5.4V的样子;当继续升高电压的时候,OUT的电压会缓慢上升,到23V的时候,OUT脚输出电压会到7V。

如图,VDD为芯片电源,OUT为输出电压。当电源电压在12V~20V的时候,OUT的输出和设计值一样,大约是5.4V的样子;当继续升高电压的时候,OUT的电压会缓慢上升,到23V的时候,OUT脚输出电压会到7V。做probe验证,npn基准的电压没有随着VDD发生变化,那OUT脚的电压为什么会发生变化呢?

随着VDD发生变化

在12V~20V的时候,输出电压值是恒定不变的;超过21V的时候,电压就会缓慢上升。

VR是个什么diode?

VR是个基准电压,5V的基准产生的啊

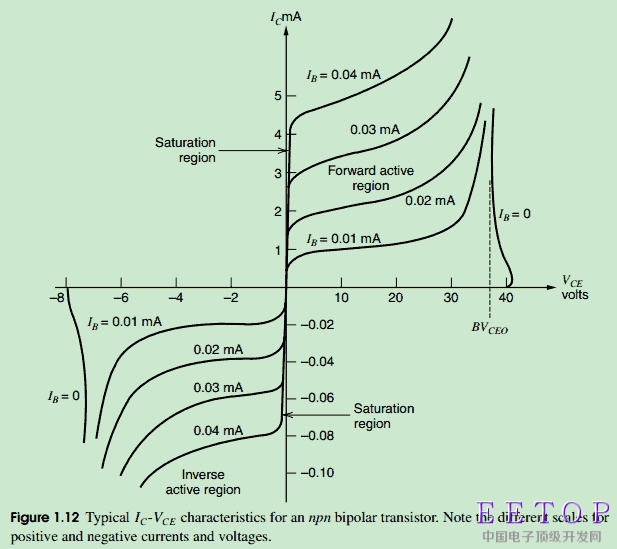

会不会可能是当VDD大于21V后, BJT开始发生雪崩击穿, 使得Ic电流增大, 从而使输出电压上升.

应该M=30那个 BJT 的ie电流变大了,是什么原因?需要查fab文件和layout了。

查一下npn的BVCEO是多少,VDD增大后应该是接近这个值了吧

你的意思是,CB极的NP结已经被雪崩击穿了?所以才导致IC上升,电压上升么?

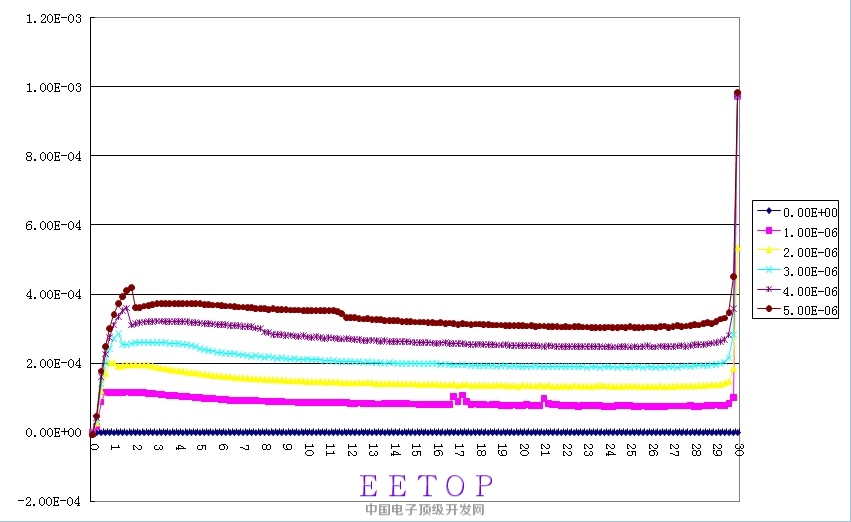

Ve=0,调整Ib=0uA-->5uA,扫描VC的电压值,观察Ic什么时候出现跳变。

从结果来看,Ic出现跳变的时候应该是接近30V了,这个该如何解释呢?

从你的现象看是BVce应该在16V左右,这和fab给出的曲线不符。

再次确认一下,两边的npn是不是相同的。

顺便问一下用的是哪家的工艺,如果方便的话。

恩,这个是上华的1um40v工艺,npn三极管的耐压我们自己调整过工艺的,这个数据应该没有问题,就是在wafer上面测试出来的。唯一的区别就是测试的时候Ve是接0的,电路里面不是的。

和我的测试结果一样,我也用了这个工艺。

和npn中流过的电流(Ic)有关,如果降低ic,耐压就上去了。

你们调过参数,但应该大同小异。

在Vout处挂一个电阻作为负载,看看Vout是否随着负载阻值变小而回复正常?

耐压和晶体管有没有流过电流有很大关系的。

MOS是这样,BJT估计也一样。

关键是我现在输出上面没有负载,只接了一个10nF的电容倒地,应该没有多大电流的说。

挂了负载,输出电压会下降一些,但是电压上升到一定程度后,还是会继续往上升的。

ENB 是接的哪 多少V 随不随VDD变化

感觉是M=1的BJT的Ib有随VDD变大

提供一个思路,你测试时监控VCC的电流,当VOUT出现异常时IVCC是否也增加?此时很有可能是寄生pwell/BN/Psub 的PNP通了。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。