DC-DC负载调整率差的问题

不会扣信元的

没有牛人出来指点一二吗? 牛人呢?

掉下来的详细时间参数,感觉像是环路带宽

目前我调整了一下误差放大器输出的Rc,Cc补偿零点, 一般来说,小电感DC-DC中只要设计这个补偿零点与你的输出次主级点相当就差不多了.而且我的确是这样做的. 而且主级点目前非常小了,10几HZ, 如果我的环路DC GAIN有60DB,那么我的GBW应该有10几K了,也够了啊,应该,而且右半平面零点fRHPz最极限大概70KHZ处,离我环路带宽也挺远了,难道是我的DC -GAIN不够导致GBW严重下降>?晕!死这样的话就不知道怎么弄了. 我在回去把我的传输函数建立起来求以下DC GAIN在来看看了.不过我用1.23和0.6的基准做为EA的VREF都试过.,,效果一样.

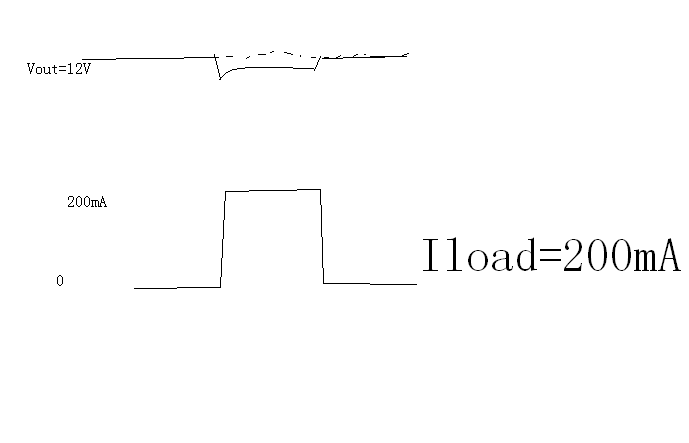

现在的波形变成了这个样子了脉宽50uS ,T=100uS )

你仿真LOAD regulation 没有, 看看在从0mA ~200mA, 输出电压相差多少, 如果和瞬态仿真的稳态一样,说明输出阻抗太大,要提高增益,减小输出阻抗,才能获得较好的负载调整率, 你的补偿结构什么样的,可以看看嘛?

谢谢楼上建议,负载调整率还未计算,只是仿了一下负载从20mA变到200mA时和负载从200mA变到20mA的输出的变化.从0变化到200mA时,输出电压可以很快调整过来,但从200mA变化到20mA时,输出调整就很缓慢,远远低于10KHZ带宽..估计只有5KHZ了...

some thing go satrurated?

just check all the control signals along the control loop. you should be able to find out which point is abnormal.

要么就是反馈环路阻尼过小。要么就是积分项没有,导致无法抵消静态误差。

貌似不是这样吧~~一般都有两个极点 一个是你说的 一个是输出极点

两个极点都有可能是主机点

如果你加的负载电阻增大,很有可能另外一个几点变成了主机点。

另外出现你这样的问题貌似是BWG不够的原因。如果没有出现振铃,那是因为速度还不够快。

感谢楼上各位的讨论, 目前找到问题了.主要原因还是斜坡补偿的设计不当造成了带负载能力差,

,前馈电容也小调整了一下. 重新调了一下斜坡补偿可以看见轻微的振铃,

9楼的哥们说的不错,两个极点都有可能成主机点,所以内部Rc,Cc的补偿就非常灵活和重要,你看目前

很多DCDC的RC,CC补偿都是通过COMP口外加的,就是给用户去根据应用的不同条件负载去调整,

一般这玩意都比较大.因为他作为主机点是比较理想的,GBW不会因为负载变化而受很大影响,至少

右半平面零点不会对你系统造成威胁而已

长知识了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。