带隙的稳定性问题

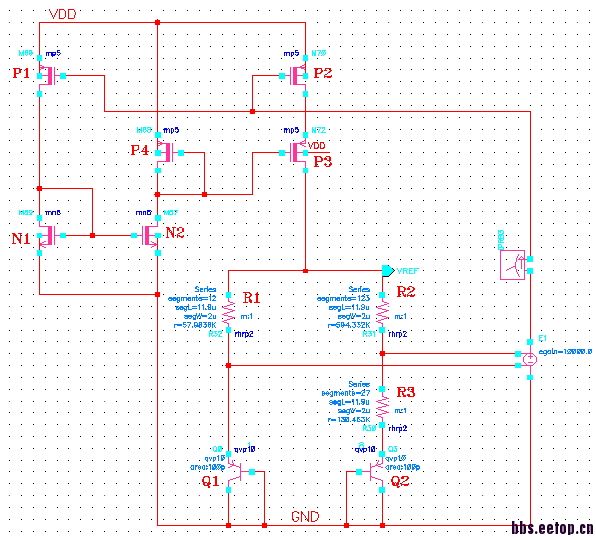

我搭建仿真电路如图所示,我想看下带隙的反馈环路是否稳定,于是,用理想OP(gain=10000)和stb仿真了一下,用stb看Phase Margin和频谱波特图,相位只有10多dB,后来把stb去掉,把VDD变成从0到5v的跳变,直接看VREF的瞬态,发现一直是在振荡。

我想请教大N们,你们做带隙的时候,环路稳定性是怎么分析的?

帮顶一下吧,同学习

我后来把理想OP换成自己的运放结构,在运放输出端接stb仿真,调好指标,Phase Margin:67°,Gain=100dB,Gain Margin:9dB,加启动电路的时候,还是会产生振荡,无法稳定。

请问哪位碰到过这样的问题?恳请指教!

你这个结构有什么好处,提高电源抑制比么。感觉比较奇怪。你这个电路除了运放,比一般的基准结构,多引入了2个极点,很容易震荡。

直接用一个P管能保证PSRR高吗?我没经验,求指导

只用一个pmos,用长沟道也能达到80db的抑制比。

进一步提高的话,需要用另外一个基准来作为电源

PSRR要-90dB,用cascode应该没啥坏处吧

VREF震荡时,你的那个P2/P3gate怎么样子的变化呢? 你是否可以给P3gate一个固定偏置电压。

带隙是给别人提供偏置,怎么加固定偏置啊

反正你这种结构在运放的基础上又多2个极点。尤其是R1 R2这个位置,电阻有500K,这个电阻太大了,产生的极点离原点很近,严重影响稳定性。

还有一个更严重的问题,如此大的反馈电阻的负载效应,会在输入节点产生一个不能忽略的输入极点,你这个电路能稳定才怪

我的肤浅理解,可以从这几方面来考虑,首先是采用共源共栅输入,减小输入管的米勒效应。运放采用三级结构,包含缓冲输出级,降低输出电阻,这样的话,可以使用低电阻反馈网络。输入信号不能有太高的输入阻抗,否则的话也要加缓冲器。还可以使用开关电容结构,这样就不考虑反馈网络的负载效应

基准架构中你确定要用三级运放么? 如何能保证基准的良率?

哦,我没有认为你是要把运放用到bandgap。bjt的偏置你用的哪种结构?如果是mos偏置结构,电阻可以很小。如果是电阻偏置结构,运放采用折叠式共源共栅+缓冲输出级的二级结构,反馈网络用1000欧姆的电阻也没问题。

1000欧姆的电阻?那么流过该电阻的电流大概有600~700uA的值~然后。

哪里有这么高的电流,只是最小的电阻1000,另外一个5000左右,电流不到150u啊。如果电阻2000和10000,那就更小了。

才150u!?

你觉得电流是多大。我们似乎讨论的不是一个东西。电阻上的电流为vt*lnm/R,如果R为1000欧姆,m为40,电流大概100u

我们做项目的带隙,PTAT电流一般设成10u或者20u,100u+也太大了吧

20u电流,电阻也才5000欧姆。你的电路的相关电阻好像上100k以上了。

随着VDD发生变化.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:PFD型PLL设计遇到的问题

下一篇:只用nmos能实现pmos电流镜的功能吗?