PLL jitter 测试过大,如何优化?

录入:edatop.com 阅读:

charge pump PLL

LPF 就是简单的二阶滤波器。

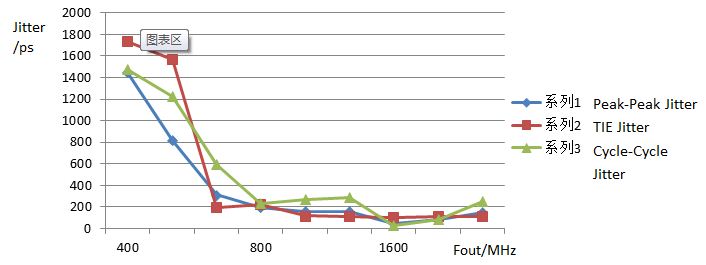

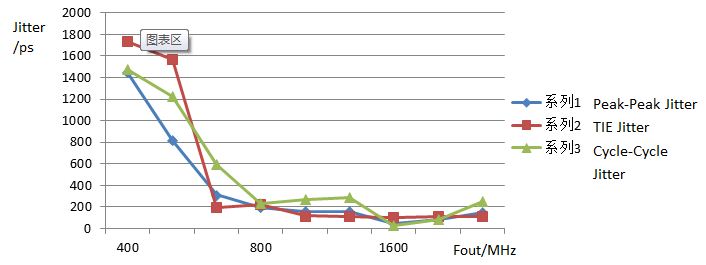

基本的功能都正常,但是就是jitter有点大,特别是环路工作在低频段。

求各位大侠指导。

另外,还有一个奇怪现象就是片子测试后放置一段时间后再次测试,出来的频率整体偏大,而且是前期测试的时间越长的出来的频率偏离理想值越大。

各位大侠,

帮我看看

LPF 就是简单的二阶滤波器。

基本的功能都正常,但是就是jitter有点大,特别是环路工作在低频段。

求各位大侠指导。

另外,还有一个奇怪现象就是片子测试后放置一段时间后再次测试,出来的频率整体偏大,而且是前期测试的时间越长的出来的频率偏离理想值越大。

第一个问题也太大了,让人没法回答。

问题描述不清楚,没有具体点的测试结果。无法回答

要有实际测试结果才能分析的嘛

笼统。

工作在低频段什么意思?是说输出频率低么?那参考频率有变么?

jitter大 指的是 jitter in time 还是 jitter in UI?

這問題很難

测出来的jitter大,首先假定是ring pll,则在低频端测出来的jitter大恨容易解释就LPF的输出电压接近

V2I电路的输入管的vth值,测得越久频偏越大可以认为是vth在略微升高。

pll输出频率高点会好点,利用分频器输出,这样的话vco输出的频率高

最好把问题描述清楚些,别人好帮你。

各位大侠,

帮我看看

用的是哪种结构的VCO?不同频率下loop有调整吗?

用的是查分结构的VCO

这个版本的的LOOP是固定的

这个jitter过于大了,以至于我认为它是由于电路设计有问题引起的。看看phase noise之类的频谱先看看是哪种成分的影响在起主导然后再做判断。

学习学习

做过VCO Pnoise 分析,发现有两个管子1/f noise 偏大 在1KHz,

在1MHz 左右有id热噪声占主导,但是现在还是-103dBc. 是不是还是有点大啊?

顶起!

jitter spec. ?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请教——VCO输出的buffer问题

下一篇:mom-cap电容的寄生电容如何仿真