基于PLL的CDR Verilog-A建模求助

录入:edatop.com 阅读:

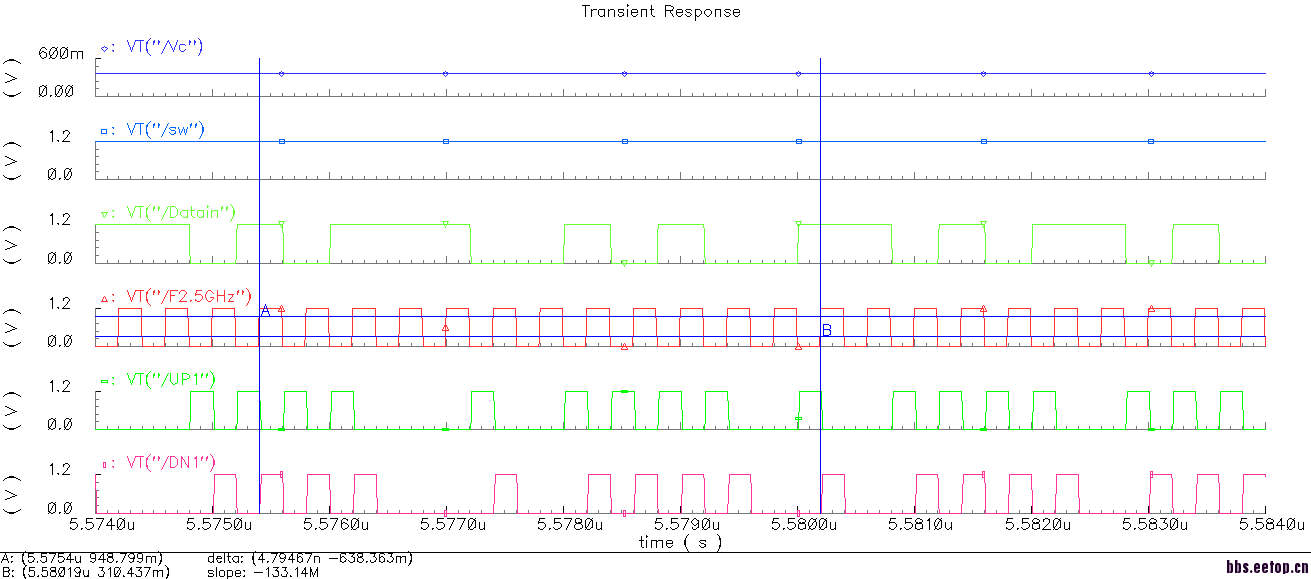

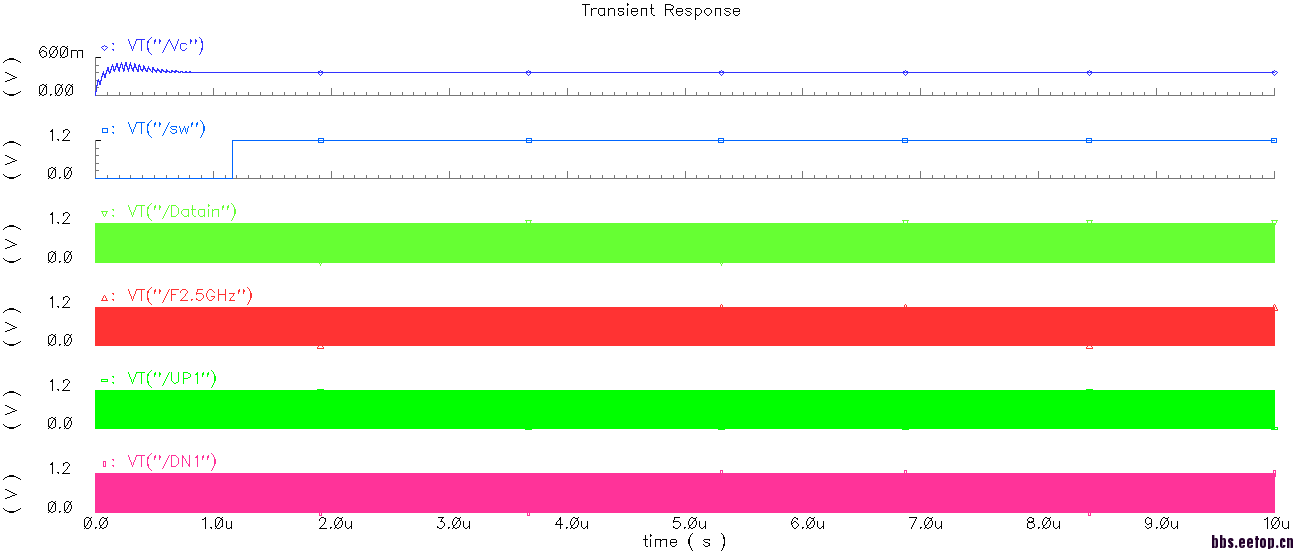

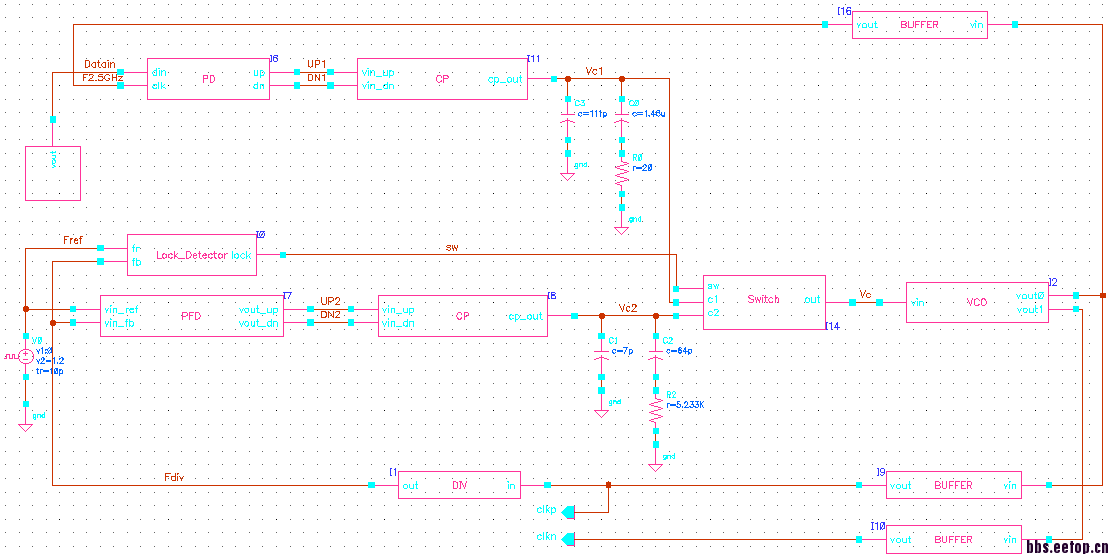

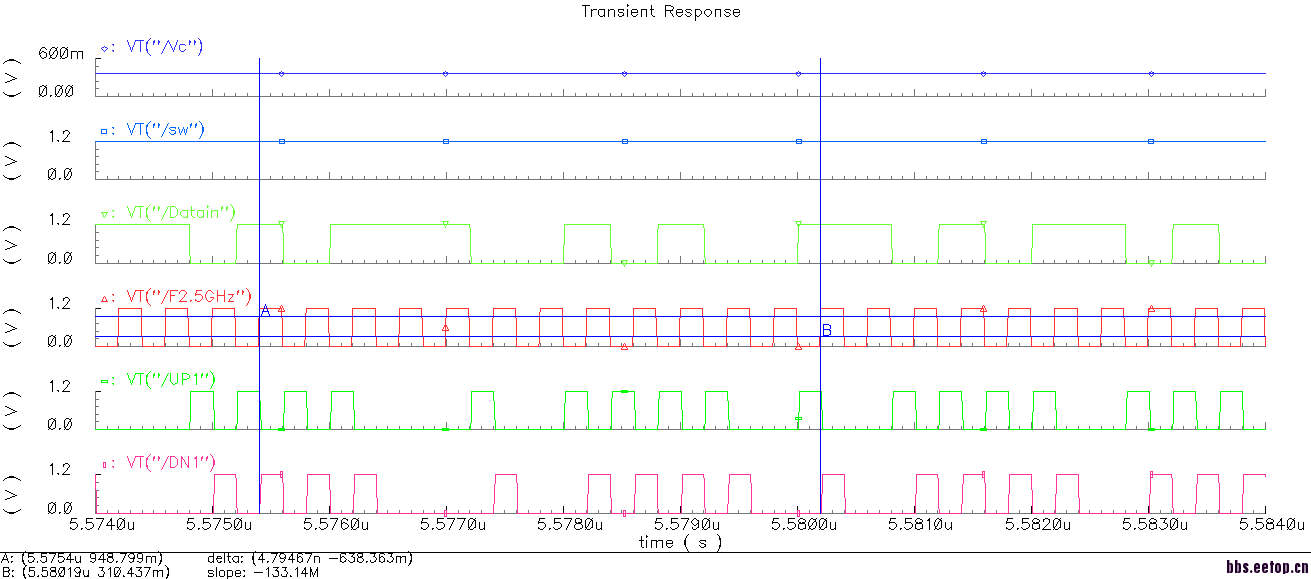

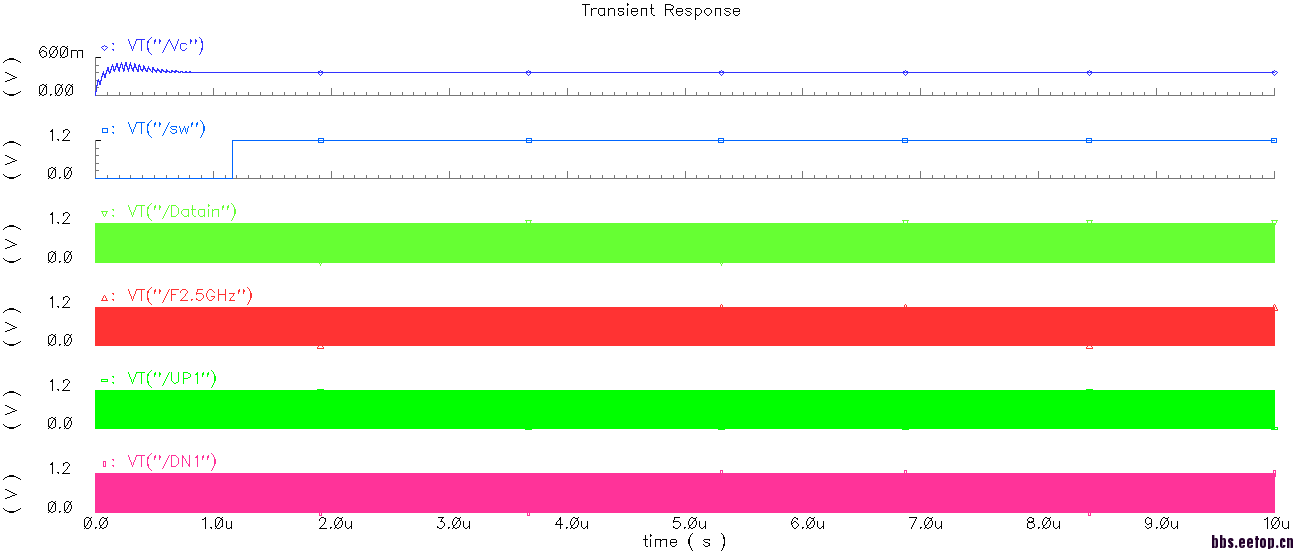

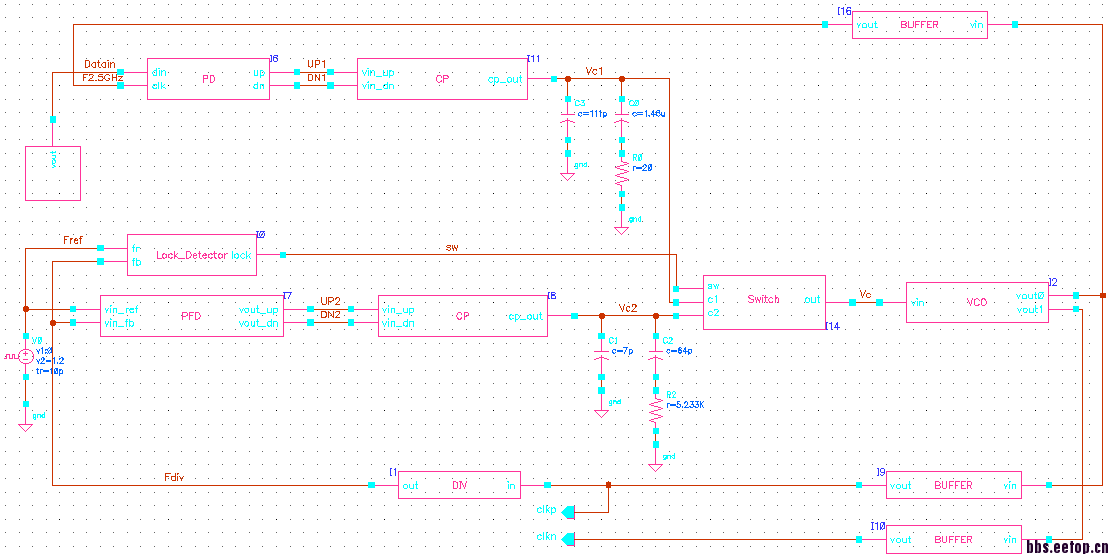

本人在Cadence上用Verilog-A语言建立了基于PLL的CDR行为级模型,为什么只有在鉴相器两个输入端的频率(2.5GHz)完全相等的时候才能锁定呢?可是实际应用的时候输入频率肯定不能完全等于2.5GHz的,而PLL频率却会恒等于输入参考频率(25MHz)的100倍啊。这样实际应用的时候岂不是锁不定?

2000-3000ppm误差是允许的

取决你的带宽

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。