ESD触发电压太大会不会引起ESD失效?

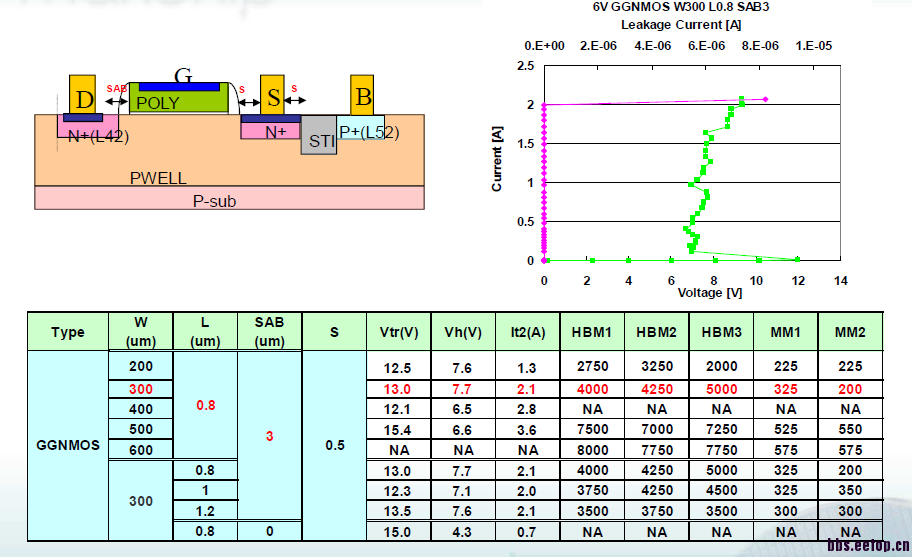

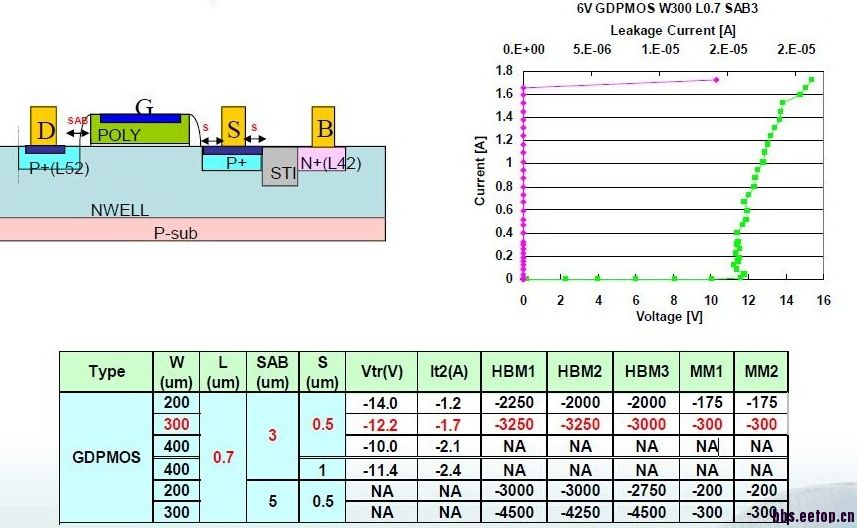

如上图所示,小编最近做的项目里面FAB提供的GGNMOS、GDPMOS的触发电压都是10V以上,而系统是6V的器件,击穿电压很多都在在8-10V,求问,这样用这个GGNMOS、GDPMOS做ESD不会还没触发就击穿了吗?欢迎各位指导。

trigger电压过高,风险很大啊。

6V器件的击穿电压8~10V,你说的BVSD还是栅氧?

BVDSS,栅氧是13V左右,这里面GDPMOS就是12V以上了

差不多了。栅氧击穿是直流,而ESD是瞬间放电。如果ESD的开启电压太低了,芯片的耐压效果也没有了。

普遍都是trigger电压在VDD的2倍左右,甚至更大一点

短时间内的2倍overstress不会使得gate oxide breakdown

ggnmos利用snapback特性来做ESD保护

这通常是用在在2.5V/3.3V及更高电压、更大尺寸的器件

现在的低压core device通常不能使用snapback特性来做ESD保护

谢谢您的解答,我是这么理解的,Vtri可以大于BV,但是vh不能大于BVDSS,也不能大于栅氧击穿电压,因为触发是短时间内不会击穿栅氧,但是如果泄放时候电压都大于BVDSS就可能会引起器件烧毁,比如这里面的GDPMOS的泄放时候电压就14V以上,即使多个并联也是12V以上,而普通的管子BVDSS就在8V左右,可能会一直击穿烧毁,这样理解对不对呢?

顺便问一句,现在低电源系统不能用snapback特性做ESD是因为触发电压本来就很小是吧,没有多少回折的余地?

再次感谢并期待您的解答!

是这样的,Vh高,就像那个pmos没有snapback特性就失去了ESD保护的功能

所以大家一般都用ggnmos,很少有人用pmos

对于低压器件,主要是因为ggnmos的工作原理是需要nmos drain端pn结反向击穿,注入电流抬升衬底电位来触发nmos沟道下方的npn

但是反向pn结击穿电压不会大幅度减小,所以低压器件就没法用了

比如5V器件,衬底浓度小,pn结击穿在11,12V左右,2.5/3.3V 衬底浓度稍高一些,pn结击穿降到7V左右

但是1V器件,衬底浓度更高一些,但是pn结击穿也在4~5V左右,这个是有物理特性限制的,这个trigger电压对于1V器件来说太高了

很容易还没有snapback就把gate打坏了

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于ADC的几个疑问?

下一篇:关于RTC的问题