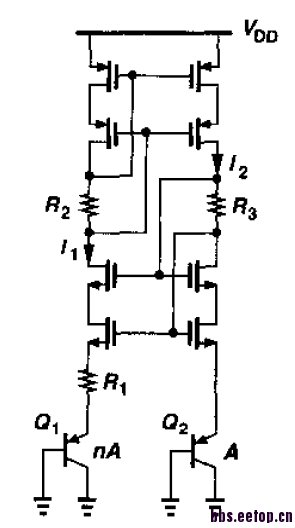

关于拉扎维带隙那一章的举例

录入:edatop.com 阅读:

我想请教下,如何分析这个电路中的这个偏置呢?

我想请教下,如何分析这个电路中的这个偏置呢?

self-bias

加上启动电路就OK了。

同意二楼······

PS 怀疑这种带隙现在根本用不了 0.18以下电源电压顶多就2V headroom大概会被上面那串“低压偏置”吃的差不多了

还有用到的,我们项目中用的就是这种架构。对精度要求不是那么严格时,该架构结构简单,不需要OP,很省面积(2.3-3.6V电源),或者说至少没有发现什么坏处。

图中采用的二极管连接方式,正是为了克服低电压应用下headroom较小的缺点(.11工艺)。

你确定?二极管接法的话源漏压差至少要一个阈值,这能省headroom?

它有跨过一个管子,所以vds被压低了啊

这叫低压cascode 不叫diode-connected

这个电压不低了!说一说0.18um以下不实用

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Cadence中的ADE是什么意思?

下一篇:关于芯片封装引线上电感的问题