为什么DCO需要归一化

版上的大神们:

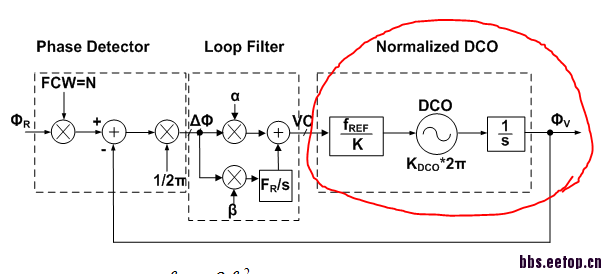

版上的大神们:最近在做一个ADPLL,看了不少文章,也做了一些行为级的仿真,遇到一个问题,即DCO为什么要进行归一化,如果需要计算带宽的话,可以直接进行计算啊,没有必要进行归一化啊,我看了Staszewski的书,还有一些其他人发的文章,都把DCO进行了归一化处理,谁知道为什么要进行归一化啊。

求指导!

谢谢!javascript:;

有人回答吗?

怎么还没有人回答,有人做ADPLL吗?

我看到的是说考虑PVT的变化,做归一化之后环路的带宽等就与PVT无关了

我觉得不做也可以,只要保证在最坏的情况下,ADPLL的性能如锁定时间、相位噪声等也能达到要求就行,有些论文中也没有就行归一化。况且Staszewski是针对射频收发机做ADPLL,每个传输的数据包之间有时间来做归一化,并且按照他的做法需要用到除法器,我想应该是要利用到收发机基带部分的DSP(他的书、论文什么的最后给出的芯片都是整个收发机的芯片,是他在TI的时候做的),而单独做ADPLL条件可能不具备

太谢谢你的回答,我现在还在纠结中。

不好意思,这几天没有看到。在ADPLL中,有很多地方会有移位和数据溢出的情况。怎么知道DCO的控制字的位与PHASE Error的位之间的对应关系呢。比如原来如果PHASE ERROR=2,DCO的控制字为10000;如果中间存在移位的话(我觉得移位其实很复杂),可能PHASE ERROR=2的时候,DCO的实际控制字可能就为01000,或者00100,这差了好几倍呢。

因为ADPLL中确实有很多的移位,所以不知道最后的DCO的控制字到底怎么对应的。

而且为什么DCO归一化了以后,就可以不受PVT的影响了呢?

谢谢!欢迎你再回复!我的QQ:317417144,可以加我QQ吗。呵呵

Staszewski的书里提出的是DCO的增益Kdco与PVT相关,而归一化除了一个Kdco,后面DCO本身的传输函数又要乘一个Kdco,就排除了Kdco对环路性能的影响,也就避免了PVT的影响

DCO控制字的位数我觉得是在做系统级设计的时候应该考虑的。需要综合考虑在各种mode下相位误差的范围,以及环路滤波器移位的位数等,以保证DCO的控制字不会产生溢出的情况。可以通过Matlab对系统的工作进行模拟

因为要two-point modulation GMSK信号,两路准确需要match

学习中。

您好,请问你提到的Staszewski的书是什么书?最近在学DCO的相关内容,所以想多看些书。谢啦!

请问,Staszewski的书名是什么?最近正在学习DCO和PLL,想多看些书。谢谢了!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:混频器转换增益和本振信号功率的关系?

下一篇:请问这个电路是做什么的