- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

国外微组装技术发展综述

航天总公司微组装技术考察团曾赴美国和加拿大,对12家从事微组装工艺和设备的公司进行考察访问。现将国外微组装技术发展动态综述如下:

一、多芯片组件(MCM)发展迅速

MCM是90年代崛起的新一代高密度组装技术,涉及许多高、新技术领域,如多层布线基板制造技术、芯片倒叩焊技术、凸点制造工艺与电镀技术、芯片级老化和测试技术及MCM封装技术等。MCM 技术发展初期,上述技术隶属于有关整机、集成电路和混合集成电路制造厂家,如今已有专门公司从事MCM设计、制造和销售,而且发展速度相当惊人。例如美国微组装系统公司MMS(Micro Module Systems Inc.)成立于1992年,是从Digital设备公司独立出来的,主要从事微组装系统设计、制造, 包括高性能MCM-D、MCM-L互连基板制造,专用多芯片组件、单芯片和多芯片封装,裸芯片和芯片级测试老化。该公司有员工300人,1996年完成销售额34万美元,同年10月该公司在硅谷被San Jose商报评为5家增长最快的公司之一。该公司的薄膜互连基板制造厂房面积7300m2,净化等级为100级,每周可生产5000片6英寸(150mm)薄膜互连基板。MMS公司的用户有著名的德克萨斯仪器公司、摩托罗拉公司、英特尔公司和东京电子等。产品质量水平通过ISO9001认证。

MMS公司制造的MCM-D具有高密度低电感、低的RC延迟等优良的信号传输特性。在铝、陶瓷或硅片上淀积多层薄膜,2.54cm宽度上可形成大于或等于1000条布线,且阻抗小于50Ω。线宽一般10μ m~20μm,间距50μm~75μm,用Cu作导体,用苯丁烷(BCB)或聚酰亚胺作介质层,厚度1.5μm~12μm。 Cu作互连导体,串联电阻非常低,而且与BCB或聚酰亚胺附着力好,因此具有良好的信号质量。

MMS公司的PCB(印制电路板)技术也有独到之处,在玻璃纤维(FR4)或BT树脂上布铜线,线宽 100μm,间距90μm,通孔直径200μm。层数的典型值为4~10层(或更多),工作频率66MHz~100MHz。

MMS公司利用薄膜技术的优势,研究和开发了一种最小的封装方式,即芯片规模封装(CSP),整个封装面积仅比裸芯片面积大20%,引腿是间距为 0.5mm的球栅阵列。传统的PWB(印制线路板)焊盘间距为300mm,衬底内最多2层布线,而MMS公司最多可以做到17层布线。衬底材料是铝或玻璃,导材是铜,线宽是25μm。

该公司与德克萨斯公司联合开发的Die Mate装置用来对裸芯片进行老化和测试,为多家半导体制造公司的CPU和存储器进行组装和封装,具有很强的技术实力。

二、芯片级老化和测试技术及已证好芯片(KGD) 技术得到实现

半导体器件的制造厂及其用户历来都是将芯片封装以后再进行老化筛选和高低温测试,这是因为裸芯片情况下进行老化和测试存在很大困难。因为裸芯片电极间距很小,只能用探针接触,再接上导线与测量仪器相连,这样带长线测试常引入外界干扰,不能得到正确的测试结果。另外,在大气中进行老化或高低温测试会引起接触点的氧化或表面结霜等问题,因此,芯片级的老化和测试,长期以来成为困扰从事微组装设计和制造人员的难题。

进入90年代,多芯片组件的出现及迅猛发展,大量昂贵的功能复杂的大规模、超大规模IC芯片要组装在一个壳体内,如果预先不进行老化筛选,封装后再进行老化筛选必然要淘汰部分不合格品, 个别芯片失效会使整个产品报废,这无疑会大大提高电路成本。所以芯片级老化和测试问题的解决就变得刻不容缓,KGD(Known Good Die)技术就应运而生。

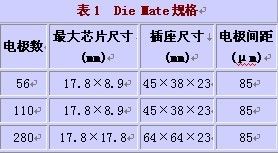

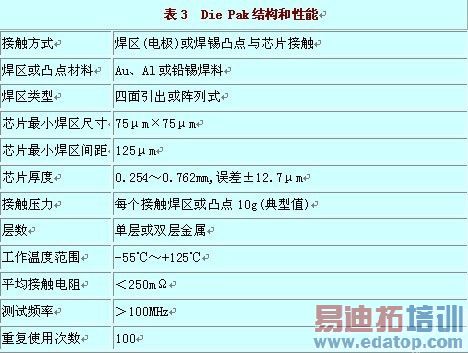

美国已有许多公司从事这方面的研究,开发出可以对裸芯片进行暂时封装的载体。这种芯片载体能对芯片起到保护作用,也不会损伤芯片电极,可以反复使用。芯片载体内装薄膜多层布线基板, 四周有微细间距的焊区,焊区上形成凸点,裸芯片倒叩在多层布线基板上,芯片上焊区与凸点接触, 芯片上方的盖板带有弹簧装置,使盖板具有弹性,盖下时将芯片与基板压紧,从而实现良好的电接触。芯片载体再装到有精细间距的插座内,插座可装到测试架或老化板上。这样就可以进行老化和全温度范围的电性能测试,合格芯片就成为KGD,从载体中取出用于组装MCM等电路。这种装置除上面提到的“Die Mate”之外,还有AEHR公司开发的“Die Pak”。其系列产品规格见表1和表2。Die Pak的结构和性能见表3。

三、凸点倒叩、凸点制造工艺及技术进入实用化

凸点倒叩焊工艺是MCM关键技术之一,能最大限度地减小互连线通路上的各种寄生参数,提高信号传输质量和速度,因此发展也非常迅速,通过凸点使芯片电极与多层布线上的焊区直接互连,从而使互连线最短,芯片组装占据的空间比其他装连方式都小,这就涉及到两方面的问题:一是凸点制造工艺,二是凸点倒叩焊技术。美国目前有不少厂家从事这些方面的研究、开发和生产,已有成熟的工艺和设备推向市场。

例如美国TECHNIC公司是一家专门从事电镀材料研究和制造的公司,创立于1945年,涉足半导体领域也有20多年的历史。该公司是一家跨国公司, 在西欧、日本、韩国、东南亚都设有分公司,年销售额达到1.8亿美元。其主要产品包括PCB板、连接器、半导体工业用电镀化学试剂及电镀设备, 涉及的工艺技术有金属电镀、化学镀、金凸点、焊锡凸点制造、晶片上镀Au、镀Ni、镀Cu等。

TECHNIC公司根据用户不同需要提供各种镀液,如TG25E或ACR434用来制造Au凸点,FBCu用来镀 Cu,93NF Sn/Pb用于制造焊锡凸点。公司设计的镀Au设备用ACR434镀Au凸点厚25μm,所需时间25 min;镀100μm厚焊锡凸点所需时间15min。

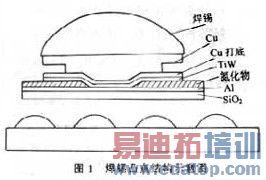

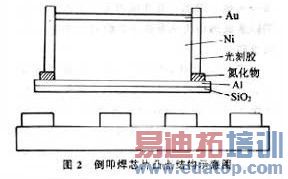

公司可提供51mm方片、φ100mm、φ150mm、φ200mm晶片的电镀设备,与QFP(四边引出扁平封装)、PQFD(塑封四边引出扁平封装)、PGA(针栅阵列)、BGA(球栅阵列)和倒叩焊芯片等产品的制造厂紧密协作,提供满足其要求的电镀、化镀材料与设备。焊锡凸点及倒叩焊芯片凸点结构示意图如图1、图2所示。

在芯片或基板上形成凸点之后,就要通过凸点倒叩焊技术将芯片与基片进行互连,实现这种互连的设备就是倒叩焊芯片键合机。这种设备已有许多公司出售,如美国KS公司、半导体设备公司等。该键合机的工作原理是首先将倒叩焊芯片与基片进行精确对图1焊锡凸点结构示意图图2倒叩焊芯片凸点结构示意图准并粘附在基片上,然后进行再流焊或通过热压(或超声)键合使其安全粘附在一起。设备主要由下列部分组成:计算机控制的可加热到350℃的工作台,芯片拾放装置、监视显示器、对准装置等。

如美国半导体设备公司推出的Model410型倒叩芯片键合机是专门用于开发及小批量生产的设备,主要性能指标如下:

芯片尺寸:0.25mm×0.25mm~25.4mm×25.4mm;

系统精度:工作台和工具温度在100℃时,对准精度为±5μm;