ADC输入信号电平怎么总体抬高

运放加法器

为什么不简简单单的插入一个source follower来做level shift?

线性度估计不够,除非像nxp那样,用feedback dac把输入信号cancell掉

何须那么复杂,只需要把vds做恒定,电流镜阻抗做高,低频输入时HD3摁在100dBc以下不是什么问题。至于高频输入的话,还得想点别的办法

这个这得看你什么工艺什么频率多少supply多少信号幅度,,,,,

那个主要是为了减小buffer的loading吧?

Twente 的办法?

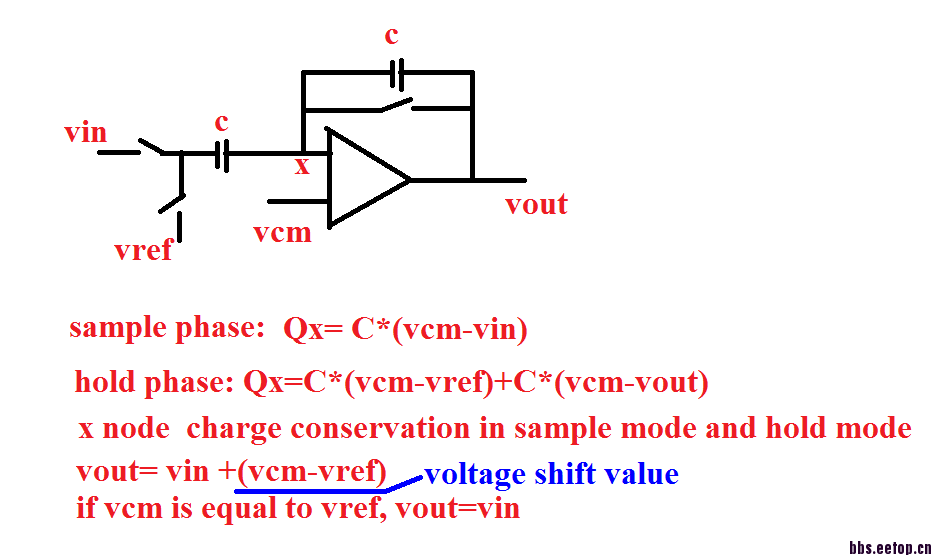

加个Switched-Cap的level shifter?

反正是ADC,电位平移直接做在sample/hold电路里面,避免了加buffer,level shift等电路的代价和引入的不良因素

加法器输入阻抗不够吧,有误差

能具体讲下吗,不是很明白

你的输入是单端还是差分信号?

source follower 电流源阻抗做高比较困难,后级要是有T/H的话 考虑到对采样电容的摆率 需要大电流 如果电流源的L选的比较大 那么source follower的尺寸会非常大的 如果阻抗不够 增益又不理想

这种结构应该可以,我仿真看看

做一个SHA应该要比做buffer和level shift的代价大太多了,毕竟一个闭环一个开环

这个到未必,sample/hold比buffer和level shift的harmonic distortion要容易做的多

一个是处理离散信号,sample以后的hold是一个settling的过程,近似于处理静态信号

一个是处理连续信号,需要时刻track输入信号,在高频输入时的harmonic太大

adc有输入input buffer的往往功耗大于sample hold,而且高频distortion还来源于此

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:PA加Bondwire会起振!

下一篇:请教NMOS可靠性问题