1.5比特ADC中比较器的设计

录入:edatop.com 阅读:

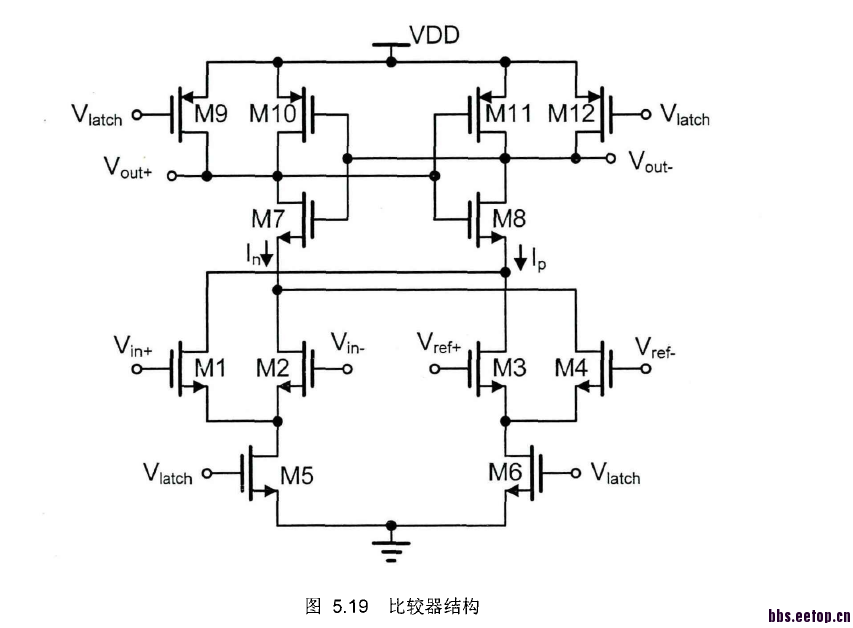

最近在做流水线型ADC,在仿真1.5比特ADC中用到的动态比较器时,对其动态比较器的原理不够理解,希望大神们指点一下,小生感激不尽![attach]631555[/attach]

图(1) 图(2)

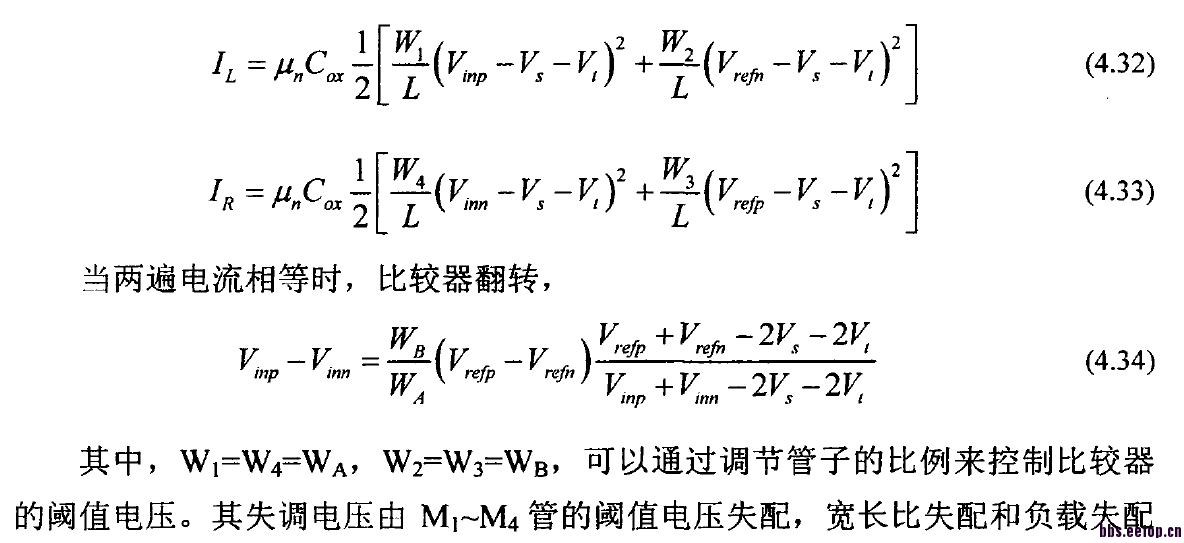

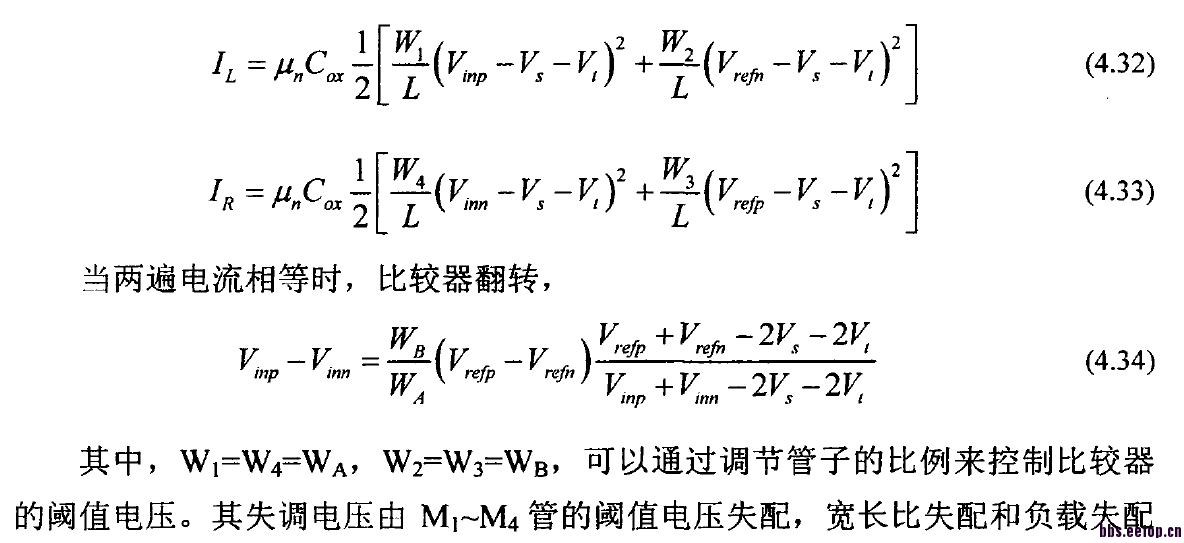

论文里说只要调节M1、M2、M3、M4管子宽的比例就可以控制比较器的阈值电压。1.5比特ADC中的比较器需要讲输入信号与-1/4Vref、+1/4Vref比较,

根据图(2)的公式,这个比较器实现的功能是不是讲输入的差分信号(Vinp-Vinn)与-1/4Vref、+1/4Vref比较了?如果是这样的话,是不是将M2、M3管子的宽设置为

M1、M4的1/4倍。?这里面输入的既有差分信号又有-Vref、+Vref搞的我都晕了。希望大神们指点迷津,谢谢了!

图(1) 图(2)

论文里说只要调节M1、M2、M3、M4管子宽的比例就可以控制比较器的阈值电压。1.5比特ADC中的比较器需要讲输入信号与-1/4Vref、+1/4Vref比较,

根据图(2)的公式,这个比较器实现的功能是不是讲输入的差分信号(Vinp-Vinn)与-1/4Vref、+1/4Vref比较了?如果是这样的话,是不是将M2、M3管子的宽设置为

M1、M4的1/4倍。?这里面输入的既有差分信号又有-Vref、+Vref搞的我都晕了。希望大神们指点迷津,谢谢了!

建议换个带有前置预放结构的比较器,精度高一些。

大神可以解释一下吗

这种结构回馈会很大吧

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。