学习pipelined ADC 中MDAC时,遇到问题求助:

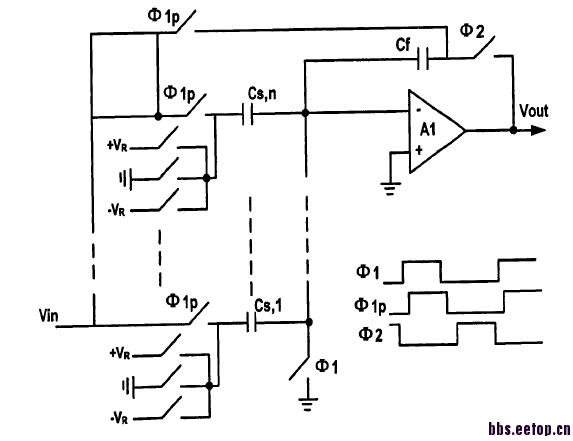

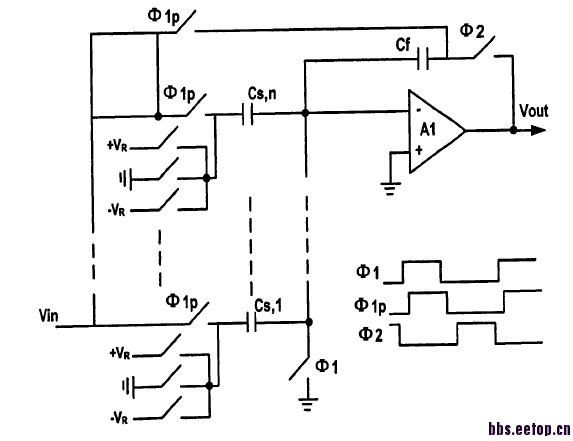

1、第n级子ADC在该级H相位完成ADC输出,并在该相位改进子ADC中MDAC完成对VIN的采样;

2、查阅资料发现,该级MDAC中求差是在该级下一个S相位完成;

3、但求差是保持相位的VIN与该相位DAC输出之差,这是否意味着求差过程中需将上一H相位的

DAC输出延时一个相位?

这是我理解错了吗?请大家帮助指导一下,谢谢。

采样就是在采样相完成啊,子ADC的输出以及MDAC的保持和求差都是在保持相

紧挨着的两级MDAC时钟是两相不交叠的

两相不交叠时钟我能理解,即第n级保持,第n+1级采样。但是上图所示的MDAC(假设作为第n+1级S/H电路),对Vin的采样(开关信号1p)和MDAC做差(开关信号2p引入Vr)明显不是在一个相位啊。

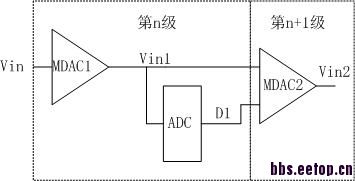

可能我表述的不清楚,重新表述一下我的疑问,如图:

1、第n级保持相位,第n+1级采样相位:

a)第n级ADC完成数字输出D1(作为开关控制位引入第n+1级MDAC);

b)第n+1级完成对VIN1的采样;

c)但是我看资料了解的MDAC结构,该相位D1并未参与第n+1级MDAC控制;

2、第n级采样相位,第n+1级保持相位:

a)第n级进入新的采样相位,无ADC输出;

b)第n+1级MDAC进入保持相位,并通过上一第n级保持相位输出D1对应的控制位,完成MDAC作差处理;

问题:这是否意味着需将第n级保持相位输出的D1延时到第n+1级保持相位?我的理解错了,还是这个MDAC就这样?

没有高手帮忙解答一下吗

如果第n级sub ADC的数字输出发生在第n+1级的保持相就可以理解了,不知道对不?

就图5而言,ADC对VIN1的采样与MDAC2对VIN1的采样发生在同一个时钟相。一般我们都是把ADC和MDAC2画到一起的。

谢谢您的回复,这样我就理解了。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:一个模拟题目

下一篇:鄙视这些不负责任的砖家