关于verilogA运放

录入:edatop.com 阅读:

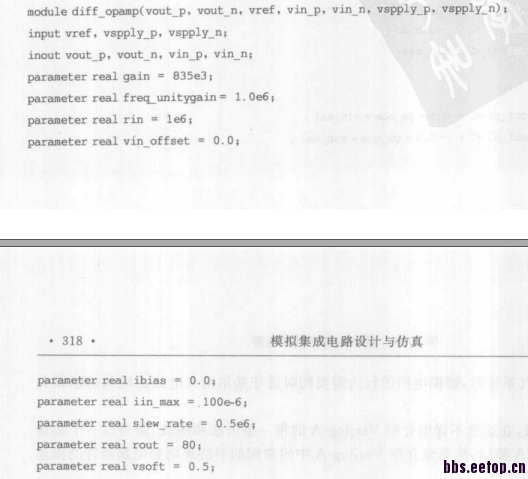

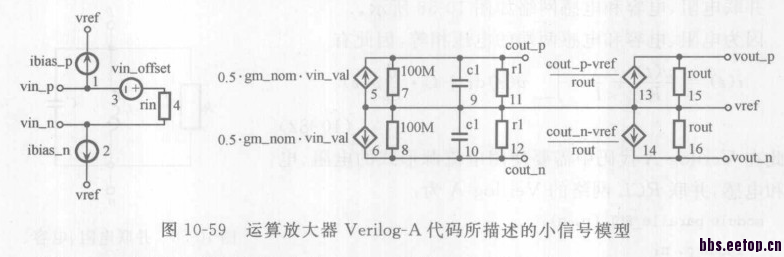

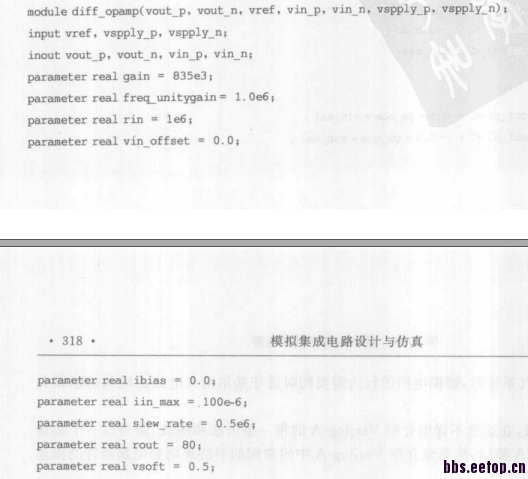

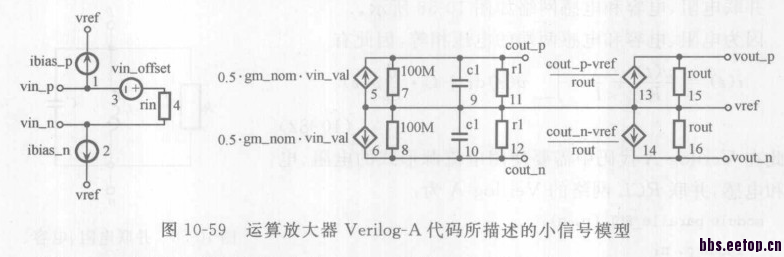

各位大侠,我用何乐年的模拟集成电路设计与仿真一书中,运放的verilogA代码,在spectre中仿真。

参数的设置完全相同,vref设置为2.5V,vspply_p和vspply_n分别为5V和0,输入vin_p和vin_n的DC偏置为2.5V,两者之间的电压差是一个幅度为0.5V,频率为freq的方波。

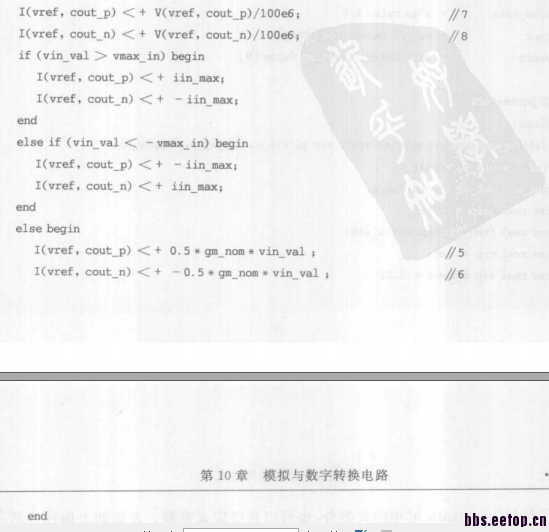

仿真发现,在频率freq大于100KHz时,Vout_p和Vout_n的瞬态波形的振幅十分小,而将频率freq降为10KHz之后,Vout_p的波形为一个高电平为4.5V,低电平为0.5V的方波(被限幅,与预期相符);但是Vout_n却是一个高电平为4.5V,低电平时4.25V的方波,感觉Vout_n的限幅不对。

不知原因为何,希望各位大侠不吝赐教!

参数的设置完全相同,vref设置为2.5V,vspply_p和vspply_n分别为5V和0,输入vin_p和vin_n的DC偏置为2.5V,两者之间的电压差是一个幅度为0.5V,频率为freq的方波。

仿真发现,在频率freq大于100KHz时,Vout_p和Vout_n的瞬态波形的振幅十分小,而将频率freq降为10KHz之后,Vout_p的波形为一个高电平为4.5V,低电平为0.5V的方波(被限幅,与预期相符);但是Vout_n却是一个高电平为4.5V,低电平时4.25V的方波,感觉Vout_n的限幅不对。

不知原因为何,希望各位大侠不吝赐教!

自己顶一下

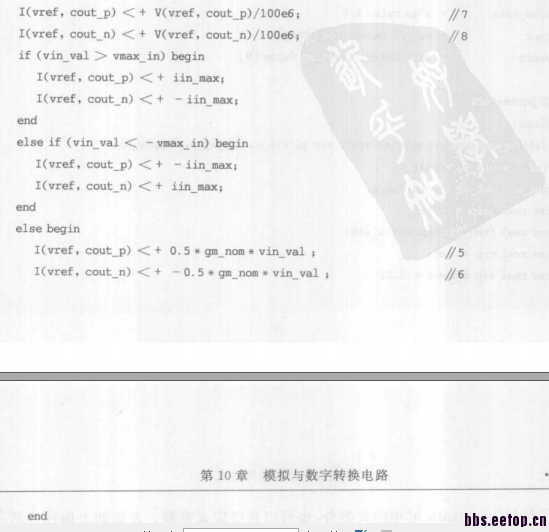

仔细看了下自己输入到spectre中的VerilogA,发现Vout_n的限幅那边写错了,更正之后,瞬态仿真结果正确。

但是,工作频率却上不去,发现C1居然有200pF

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:PCB如何画水滴形的PAD?

下一篇:如何用VerilogA编写激励信号