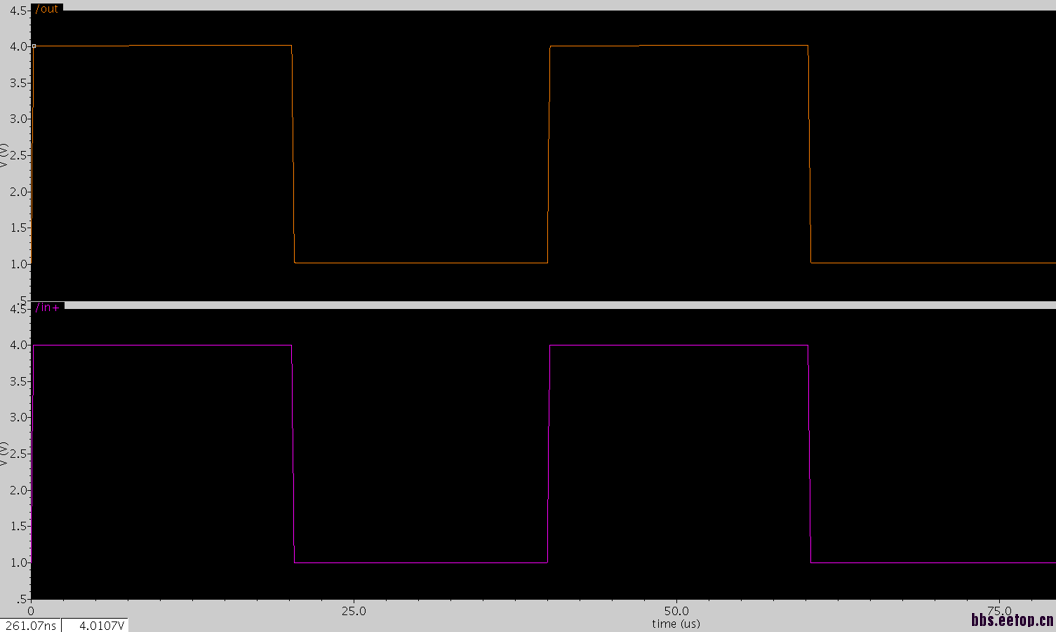

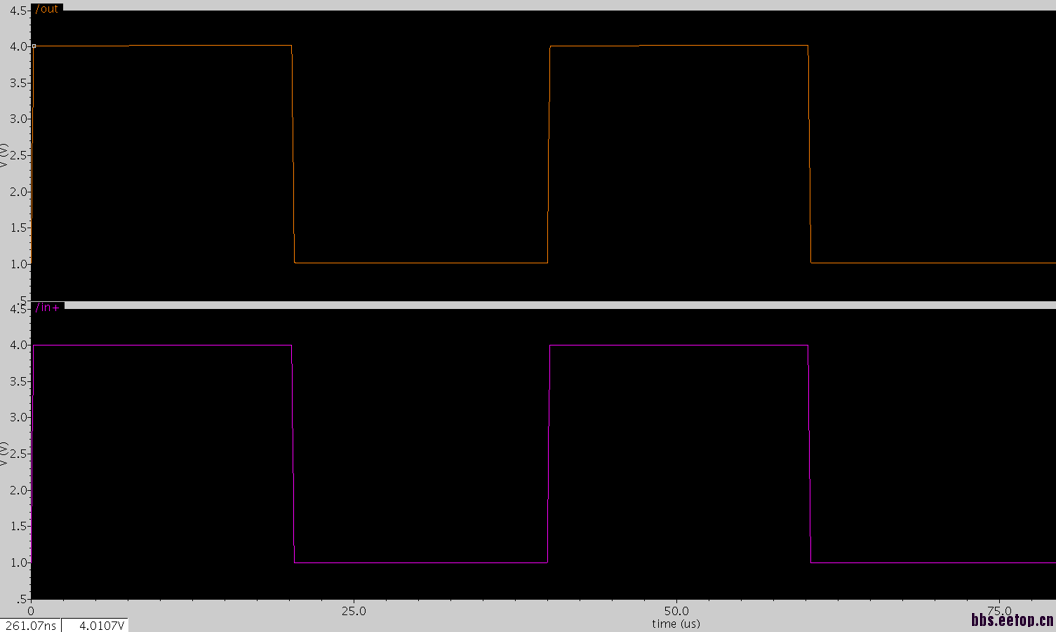

buffer的输出比输入高了0.01V,怎么破

录入:edatop.com 阅读:

- -用在显示驱动里面的buffer

理论上就算失真不是应该比输入低吗,怎么高了一点点。

求助大牛啊

肉眼基本看不出来,输出比输入很稳定的高了0.01-0.02V

肉眼基本看不出来,输出比输入很稳定的高了0.01-0.02V

开环增益有80db,80多的相位裕度

理论上就算失真不是应该比输入低吗,怎么高了一点点。

求助大牛啊

肉眼基本看不出来,输出比输入很稳定的高了0.01-0.02V

肉眼基本看不出来,输出比输入很稳定的高了0.01-0.02V开环增益有80db,80多的相位裕度

静态没调好?

为什么只能低不能高?

看个DC不就知道了,看看本来应该匹配的管子电流是否一样

大神呢?。

才想起来来top问了,已经知道怎么回事了,是有两路关键的电流失配了,调了一个关键管子的宽长比就好了

肯定是匹配的问题?

也许是

op放大器接buffer模式的话,这种情况是产生了一个0.1V的失调电压吧。也是失配引起的。

错了,是0.01V到0.02V的失调

symetric offset 一般电路设计OK 都是 < 1mv offset .

如果使用 cascode av=90~100db 可能 symetric offset sim 0.1mv .

但是 这是sim

layout random offset 是另外要算 .

symetric是什么? 说的是systematic offset?

systematic offset ..

key in error ..

sorry .

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:simulink model for Pipelined ADC digital error correction

下一篇:如何在ocean中选择montecalor的tran结果,比如mc1-001_tran.tran.dsn