Ring Oscillator (环形振荡器) post layout simulation 频率增加是什么原因?

录入:edatop.com 阅读:

用TSMC65nm设计的Ring Oscillator (加了一级buffer), simulation (pre-layout) 时的频率为1.6GHz, 但是post-layout simulation 频率不降低反而增加了(大概增加了2.5倍,4GHz左右) DRC clean, LVS match, PEX setup 都没问题,会是什么原因呢? 请高手建议! 多谢!

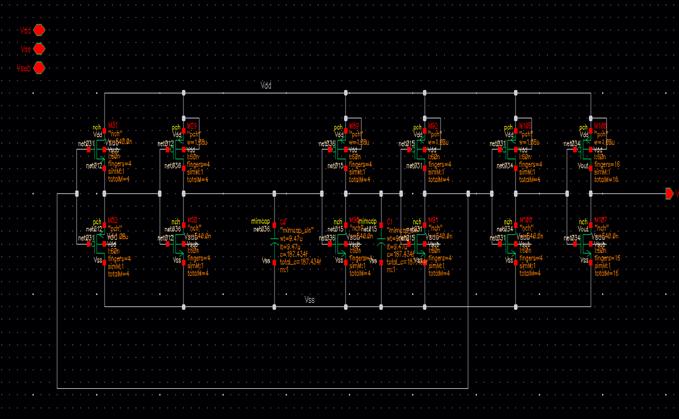

下图为schematic,第一级为buffer (inverted inverter) 为了增加延时。

怎么净是些稀奇古怪的问题

自己再仔细debug一下,肯定是哪里出错了,schematic上的第一是buffer?没见过有人这么做的,搞的像4级inverter 。自己去抽一个norc ,cc , rcc比较一下就知道了,估计就是奇葩电路遇到奇葩问题,也许对LOD, WPE太敏感了

确实很奇特

观察你的功耗估计变大了很多!

比较下PEX出来的器件W,L是否和model一致。

以前用过某pdk提出电容的长宽用c_w和c_l表示,仿真时电容认不出来,都用作默认值大小。

4级单端反相器,能做ring osc ? 需奇数级吧?

同意5楼观点,会不会是PEX提的参数不对?

四级怎么实现的

同意6楼,8楼观点。

他第一级是两个source follower

你这个电路ff corner下频率是多少?会不会是工艺偏差引起的?

哈哈,原来如此,这个其实就是三个反相器级联,O(∩_∩)O~

第一级不是反相器

大哥 你弄六级反相器 能振吗?晕 奇葩

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:ADS画PCB问题

下一篇:VCS仿真与PT不一致