Capacitor less low drop out regulator (LDO)

最近在做LDO,发现很多论文什么的都是用的PMOS,用PMOS的话LDO的稳定性很差,需要接大电容。

今天看到Sansen书上比较PMOS和NMOS结构的篇幅,用NMOS的话稳定性更好,因为接NMOS是用的Source Follower没有gain。

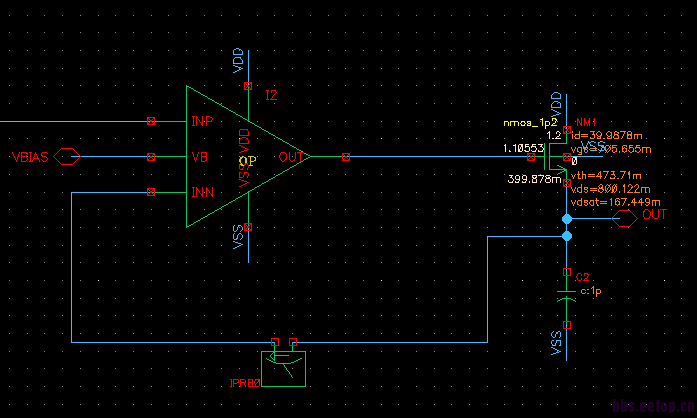

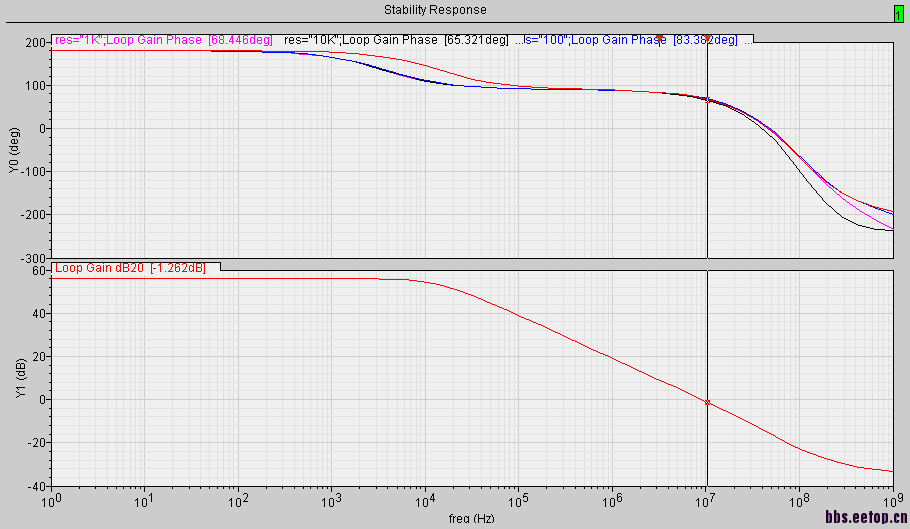

我刚才画了个电路,仿真了一下,不同负载的情况下,电容只用了1p就有很好的稳定性了

既然这么容易就得到一个capacitor less的结构,那各种各样的论文上用的那些复杂的结构又是为什么。

这么简单就得到一个capacitor less的LDO,请各位帮忙看看是不是哪里出问题了。

以下是不同负载的仿真情况,负载电流从0.04mA到40mA的stability仿真,tran仿真也验证过了,没有起振

用NMOS做输出管,没有办法做到 low dropout, 所以大部分使用PMOS。NMOS结构本身就比较容易稳定,主极点由EA决定。

谢谢回复!明白了,用NMOS的话,没法做到low drop。但是如果需要1.2V的输出电压的话,用3.3V的MOS管可以很轻松的设计1.2V的电源了,一般工艺库都会有高低电平的MOS管的,如果这样看的话,那么low drop out regulator最主要的意义是什么呢?(是当工艺不提供高电压MOS管的时候,比如130nm工艺,电压是1.2V,同时我也想用低电压的MOS管来做LDO,那我就给这部分提供1.4V的电压,然后LDO就可以输出1.2V了吗?)

40nm 一样有3.3 1.8 甚至5V的管子。没哪个成熟的工艺不提供到3.3的管子。这个就是传统的调节器,参考lm317 337一类的。

你说的好多,都被你说晕了。有时候LDO的输入是变化的,如果你的dropout太大,当输入过小后,就无法稳压了 。

按照你说的,假如带40mA负载,3.3V转1.2V,输出效率只有1.2/3.3=36.36%.

如果用low drop显然效率提高很多。不知道是不是这个原因,所以有各种复杂结构加各种补偿,用PMOS管。

哈哈,不好意思啊!LDO一般也是电源输入,所以Vin实际上变化也不会很大影响Vout,应该是像六楼朋友说的,主要是lowdrop的效率更高。

嗯,现在看来lowdrop的最大优势应该是效率高,一般都是90%以上,3.3V做1.2V的话,效率就太低了。不知道lowdrop跟highdrop(不知道有没有这种电路啊),除了效率上的差别,还有没有别的。

有高压LDO的,用跟随器结构

不是吧,3.3V转1.2V,不管用PMOS还是NMOS,效率都是1.2/3.3吧

应该是,如果你能确保你的输入电压足够高,那就好说。

LDO,名字就是 low drop output。

如果确定应用就是3.3-1.2,用NMOS是合适的,面积小,更稳定。2.5-1.2用NMOS是有点累的。所以要清楚知道应用。

LDO优势不在效率,优点就是fully integration, low noise, high density。 效率不行的

If the VOUT needs to closed to VIN(Low drop output), LDO needs uses PMOS,

and I agree with naoz's reply.

mpig

我3.5输出3.3,效率怎么不行--

还没入门

LDO的优势不是效率

如果LDO不看重效率的话,那么用PMOS跟NMOS比,优点在哪?很明显NMOS更加稳定,PMOS的drop voltage要小一些(驱动同等电流的话)。

如果用3.3V到1.2V,LDO跟芯片其他都集成在一起的话,会不会存在危险?我的意思是说,LDO起始输出可能是3.3V,这样会不会烧坏1.2V的管子?

为什么很多论文都是用的PMOS,然后用一些复杂的结构来移动pole位置,提高稳定性。直接用NMOS的话,就不存在稳定性的问题了。那么LDO里面,NMOS与PMOS的差别主要体现在Vin-Vout=drop大小上了,drop越小,效率就越高。如果不考虑效率的话,为什么不用NMOS?

你是不是还没做过实际项目,还是学生,没有人指点你,现了解一下工艺的MOS器件?

那你需要做软启动,保证输出无过冲。

1)对于3.3V的电源vdd来说,如果你要输出1.2V,那么你用nmos或者pmos都是可以实现的。效率一样低。都是1.2V/3.3V*100%

2)但是同样的3.3v电源,要输出3V的Vout,显然你这种用nmos的结构是不行的。因为驱动nmos管的gate电压最大3.3V,那么你输出Vout最大也就是Vdd-Vgs,撑死最大2.6V。除非用boost去提高nmos的栅极电压,但是显然难度很大。倘若用PMOS,显然是可以实现3.3V转3.0V输出。

3)既然要实现low drop,比如3.3V转3V,就得用pmos管,运算放大器有两个极点,加上pMOs管漏端的极点,有3个低频极点。所以需要复杂的频率补偿技术。

LDO的优势是Line regulating 和 loadregulation,其次是Input swing和efficiency。

nmos除了稳定之外,还有什么优点?

不错,看看

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于大功率功放的匹配电路的问题?

下一篇:为什么BJT的输入失调电压小于MOS