低电压系数的MOS电容底层极板为什么要重掺杂

录入:edatop.com 阅读:

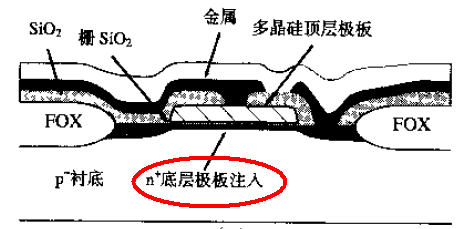

ALLEN 35页上讲为了获得低电压系数的MOS电容,底层极板一定要重掺杂扩散。小弟不懂为什么要重掺杂?见图中N+底层极板注入。

2015-6-30 11:33

使耗尽层的宽度变小,这样在电压变化时就能减小耗尽层电容的影响

这样做是不是有点像Native NMOS, 或者像耗尽型的NMOS,在栅极没有加电压时就有沟道形成,降低了阈值电压?

跟耗尽管的处理方法类似。所以耗尽管很多时候用来做电容用,在很低的电压下电容不会下降太多。native跟这个是不一样的,native的沟道是没有进行掺杂,表现出来的特性接近耗尽管而已

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:MOS超压工作

下一篇:cadence里打开电路图一堆黄色叉叉